邁向Scalable QPU-量子晶片設計

走向量子計算,整合數千上萬個量子位元是當前努力的方向。 然而,當多個超導量子位元整合在量子晶片上時,量子位元間的串擾(Crosstalk),成了當前量子計算嚴峻的課題。

中研院的量子電腦發展

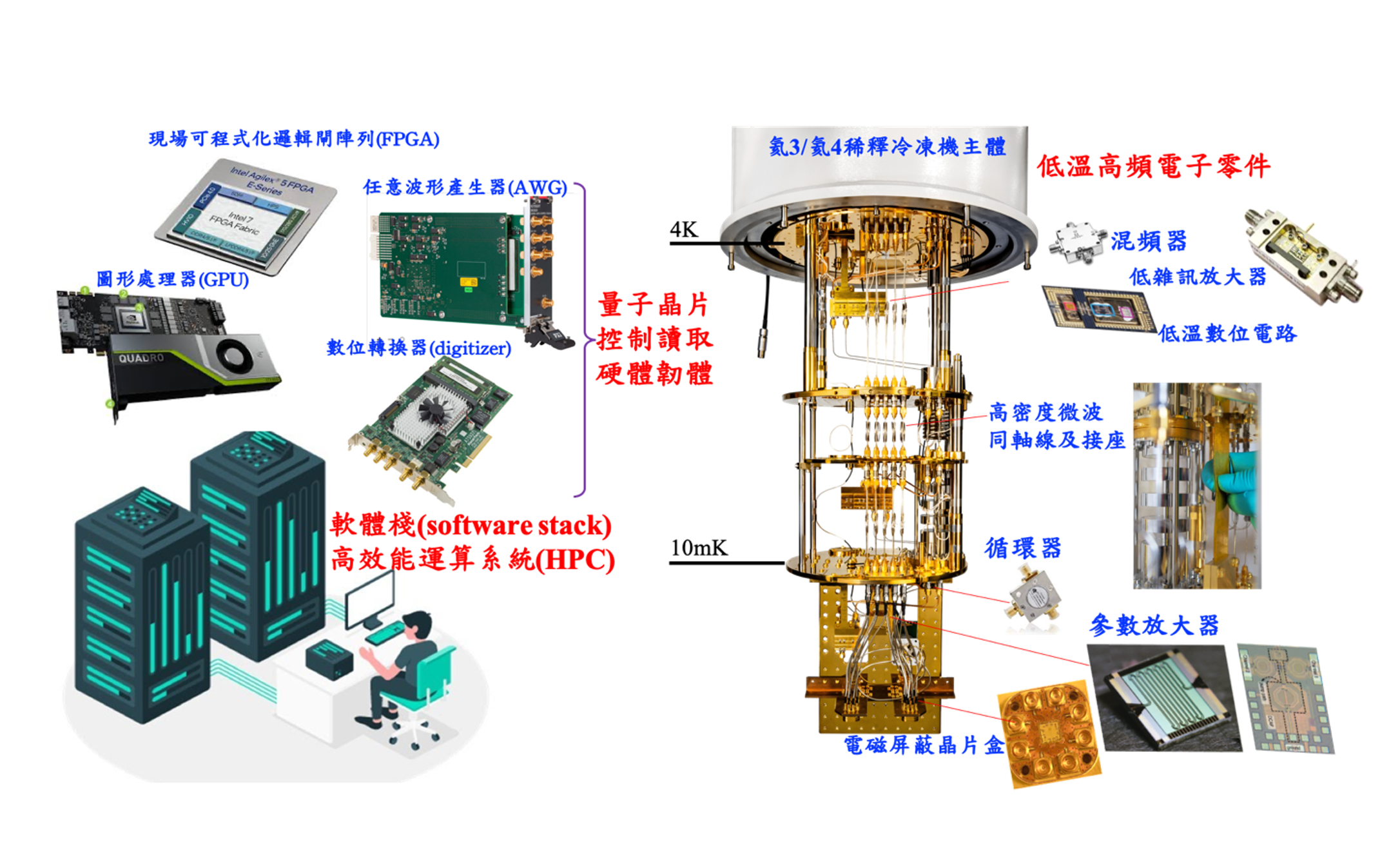

▲中研院的量子電腦解構圖,左邊為在外部的控制、分析硬體,負責將古典電腦的數位訊號,轉換成控制超導量子電腦的類比微波訊號,

反之亦將讀取出來的微波資訊轉換成古典電腦可以分析的數位訊號。

右邊為中研院採用的稀釋製冷機內部相關的微波元件、量子晶片與屏蔽組件。

Ref: Sinica

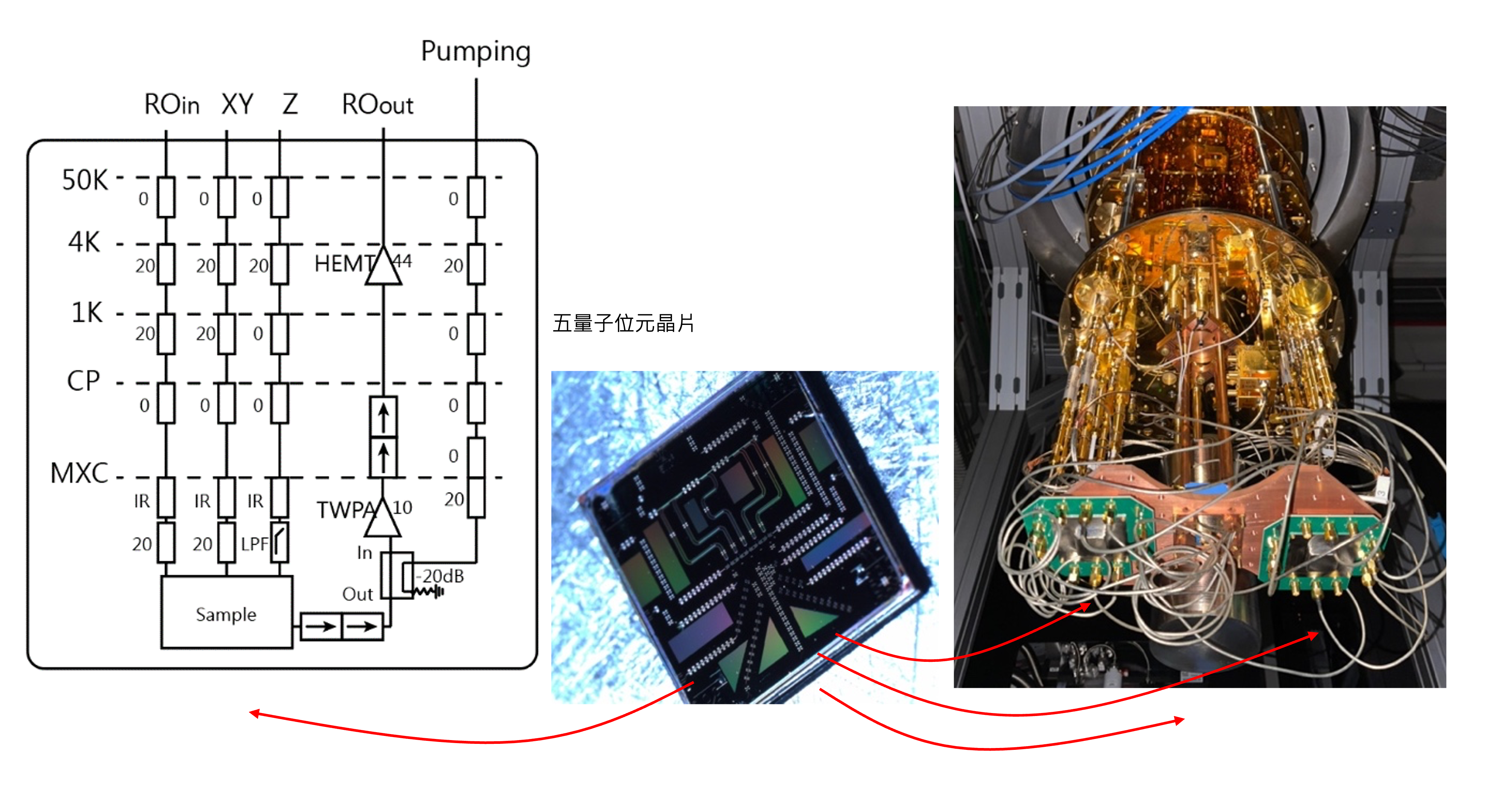

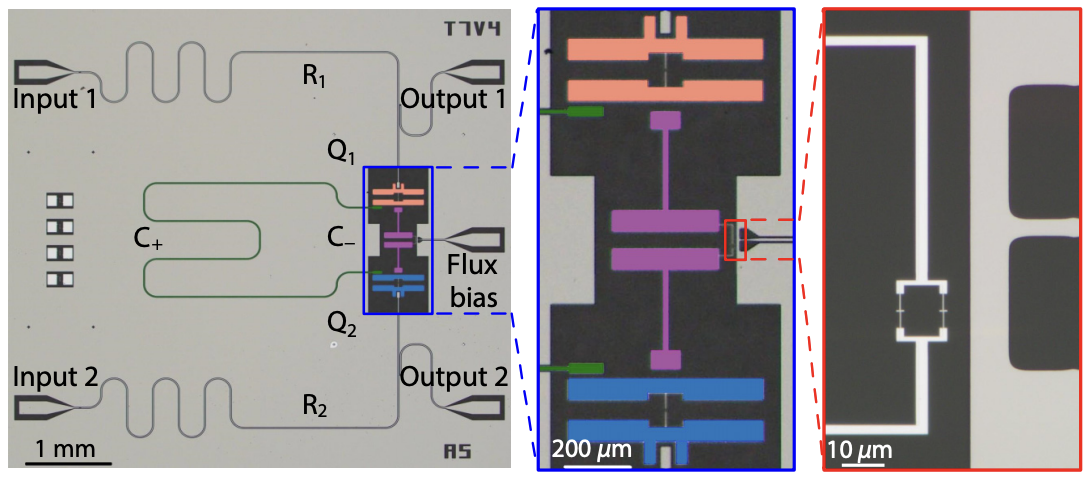

▲中研院上一代5量子位元晶片設計(據說當前在研製20量子位元QPU)。

Ref: Sinica

| I/O端 | 類似術語 | 功能解說 |

|---|---|---|

| XY | Drive line | 用於輸入控制脈衝,操控量子位元的狀態(如進行 X/Y 閘操作),通常是微波RF訊號。 |

| Z | Flux line | 提供直流或低頻訊號改變 SQUID 迴路的有效磁通量,進而調變量子位元或諧震器的頻率。 |

| ROin | Readout drive/input | 輸入微波脈衝與讀取諧振器(Readout Resonator)交互作用。通常是微波RF訊號。 |

| ROout | Readout output | 讀取諧振器會因為量子位元的狀態不同,改變透射的波段,由外部儀器分析回傳的訊號強弱來判斷量子位元的狀態。 |

| Pumping | 用於激發參數放大器(如 JPA 或 TWPA)所需的能量輸入,來增強回到外部的訊號,通常在特定頻率提供高功率微波。 |

Ref: Sinica

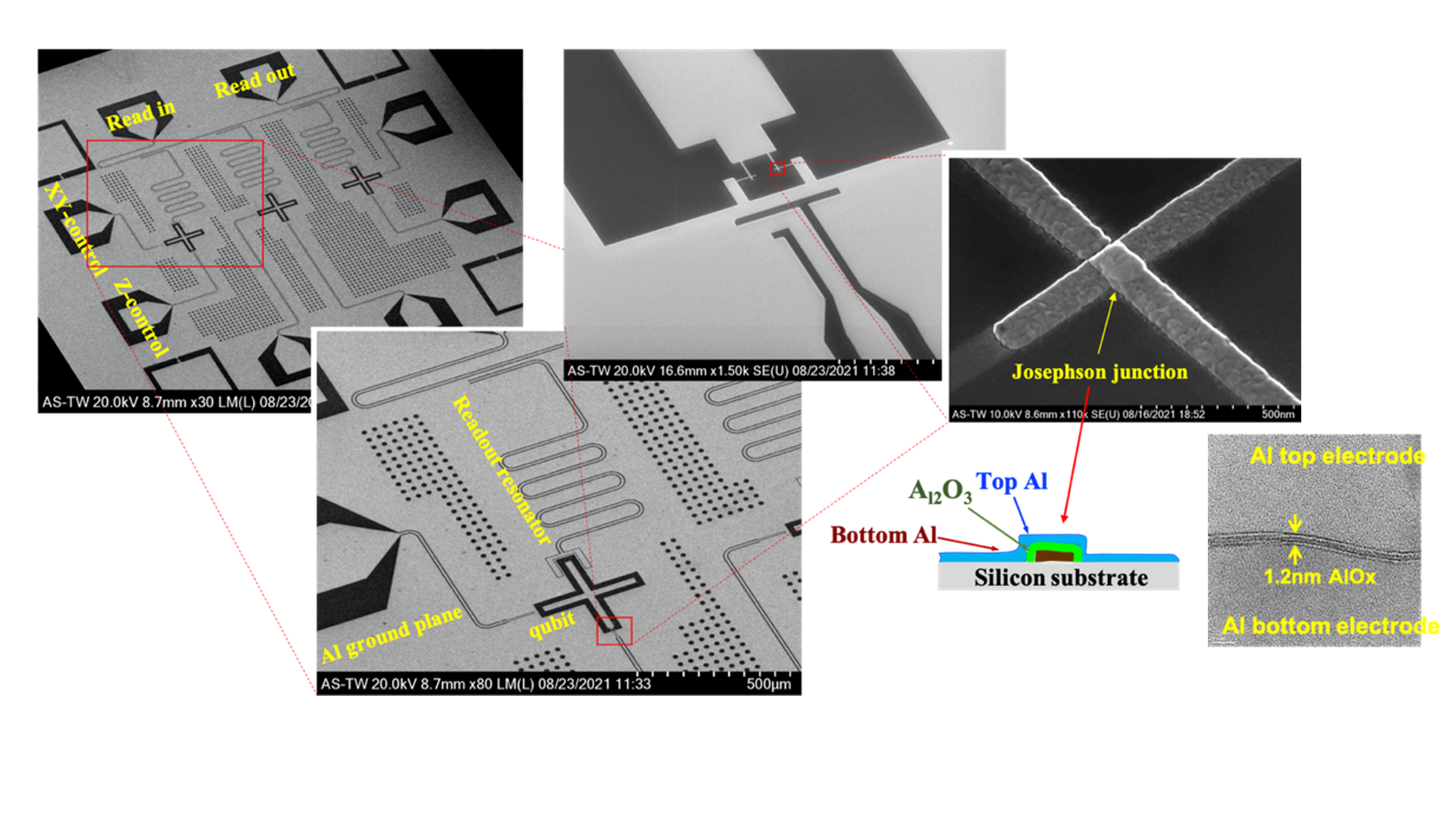

▲電子顯微鏡下量子位元電路圖、約瑟夫森節。在這邊量子位元的尺寸設計、諧振器的長度尺寸等都是設計上的know-how。

例如傳統上Transmon的設計自然頻率約在5~9GHz,這受到兩件事情的考量:

- 上限:材料的超導溫度決定了上限。目前因為鋁在製作約瑟夫森節(JJ)製程的優勢與優異的量率,多數JJ都採用\(Al-Al_2 O_3-Al\)的SIS結構為主 (相關解說可以參考「超導量子位元(進階版):約瑟夫森節」)。 鋁的臨界溫度為1.2K,意味著其超導古柏對的能量\( \Delta \)為\( \Delta=1.76 k_B T_c\)。由量子力學可知對應的頻率約為40 GHz,如果操作頻率逼近或超過這個頻率,會產生準粒子激發(Quasiparticle excitation)或破壞超導性,導致退相干發生。

- 下限:由量子電腦操作的背景溫度決定。目前超導量子電腦在的設計都處在10~20 mK,對應的熱激發頻率約為400 MHz (以20mK計算),如果量子位元設計的操作頻率與低溫的熱噪音相近,容易從基態被激發造成錯誤,量子位元設計的頻率需要盡可能減少熱背景干擾,故環境的溫度決定的下限。

依照這兩點要求,鋁基超導量子位元設計的操作頻率就被設定在1~10GHz這個數量級。(當然,如果非超導量子位元,則操作頻率可以在不同的範圍。例如矽基自旋量子位元可以在1K的環境下操作,光量子位元可在室溫下操作,對應的上下限需求就不同。) 根據操作頻率設計超導量子位元的電容能量\(E_C\),尺寸與幾何形狀需經過電磁模擬後,成為圖中的設計樣式。諧振器的長度尺寸也是由操作頻率來決定其長度。

邁向多量子位元所需要面對的問題

要達到量子計算的基本優勢,一種說法是至少需要50個量子邏輯位元(logical qubit)。此說法的根據為50個量子邏輯位元表示的計算空間為\(2^{50}\)維度, 而\(2^{50}\approx 1024 TB\)足以表示當前大部分古典電腦計算的資料量。 看起來很簡單,背後實際上要動用超過千顆的物理量子位元(physical qubit)。這牽涉到量子糾錯(Quantum Error Correction)的議題。 以Shor 9 code為例,一個logical qubit需要用到9個physical qubits+8個Ancilla qubits=17個qubit,50個量子邏輯位元至少背後有850個位元參與計算過程。 (當然Shor 9 code是早期、相對「沒效率」的量子位元糾錯方式,然而這是非常跨時代的成果。近來來已有Surface code、Color code、Bacon-Shor code等等來增加量子位元的有效利用率。) 要設計QPU,有以下議題要考慮:

古典串擾(Classical crosstalk)

量子串擾(Quantum crosstalk)

連外資訊交換(Signal input/output)

間單的說,目前一個超量子位元至少需要兩條控制線(一條XY控制,一條Z控制),再考慮讀曲線(一進一出)、泵補增益線

,如果進一步希望量子位元間的可調耦合(控制線一條),粗略就需要五倍於量子位元數量的連外RF訊號線,非常驚人。

如何排列量子位元、線路(Connectivity and Layout)

要設計超導量子晶片,牽涉到採用的超導量子位元的形式、量子位元間耦合的形式、讀取線路的需求,還有個元件之間的編排都是需要考量的議題。在這邊針對以Transmon為基礎的QPU來討論設計需求:

在這些議題上,著名的兩大陣營IBM和Google就採取了截然不同策略。IBM走的不可調路線、而Google採幾乎全可調路線。以下針對電路設計來理解這兩條路線的著眼的原因差異。

- 量子位元是否可調頻率?

- 量子位元的耦合形式

- 讀取諧振器的頻率區隔、與總線(Bus)的耦合

- 線路間的跨越、晶片分層與封裝

Ref: 作者繪製

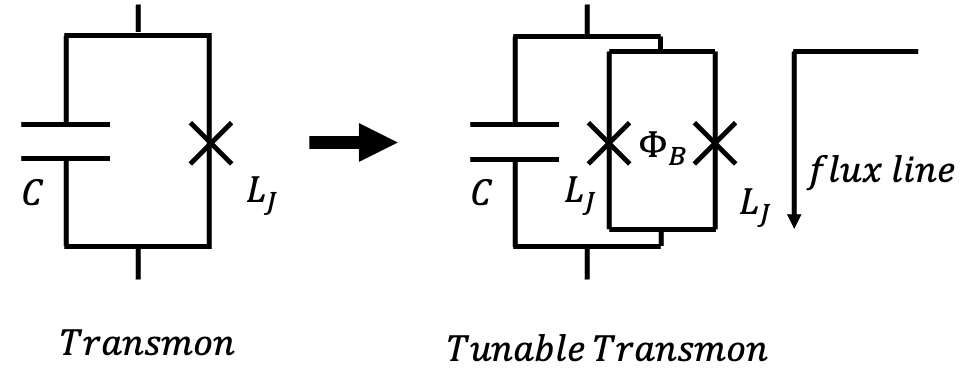

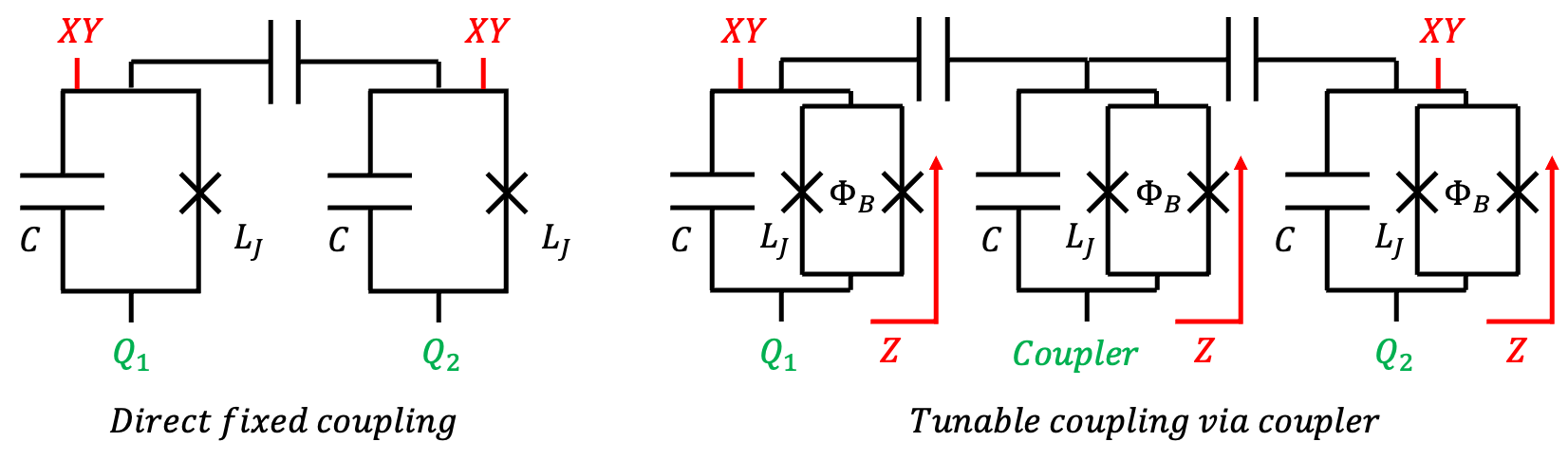

▲左側為定頻率的Transmon,由一個JJ作為非線性電感。右側為可調頻率的Transmon,兩個JJ形成的SQUID可受外部磁場\(\Phi_B\)來調控動態電感,從而調整頻率。

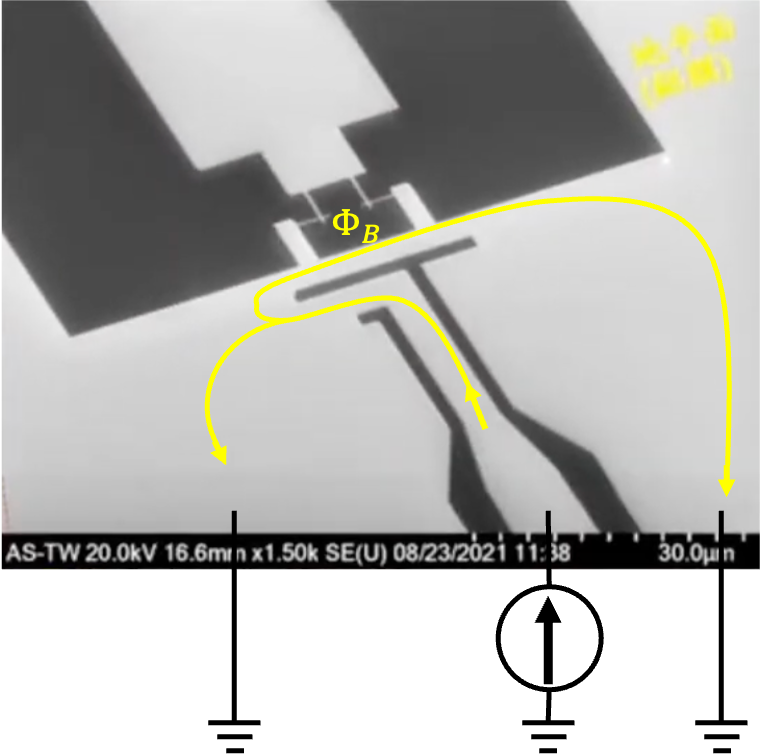

▲中研院的Tunable Transmon與Flux line (Z-Control)在電子顯微鏡下,加上電流流向的示意圖。透過調控電流的大小,產生磁場來達到調控Transmon的頻率。

Ref:作者修改,原圖取自 如何打造一台量子電腦 (中央研究院物理研究所/陳啟東研究員) https://www.youtube.com/watch?v=wceckog180U&t=3420s

▲量子位元間的耦合方式,左側為固定耦合(量子位元頻率固定、直接電容耦合),右側為全可調式(量子位元頻率可調、藉由可調頻諧振器耦合)。

IBM的固定式設計,以上圖左側為例,每個量子位元只需要一條XY-control line,共只需兩條控制線。

Google的全可調設計,以上圖右側為例,每個量子位元需要XY & Z兩條控制線,加上可調頻諧振器需要一條控制線,

就需要五條控制線,是固定式設計的2.5倍。

Ref: 作者繪製

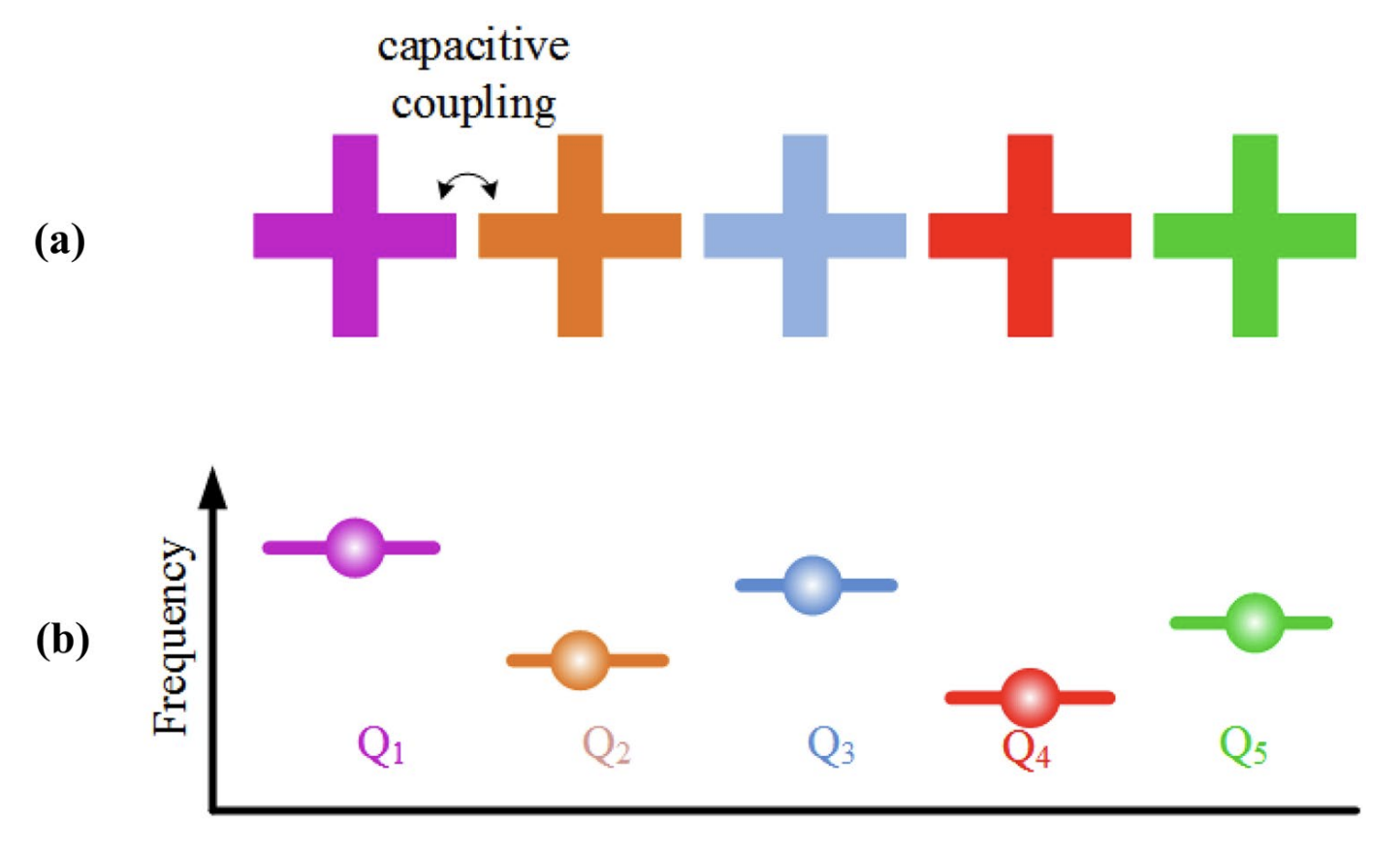

▲固定耦合式設計就需要考慮區分不同位元間的頻率分離,避免非預期地串擾。

Ref: doi.org/10.1007/s10948-021-06104-5

▲與之相比,可調式設計就可以透過改變頻率差來操作耦合強度。

在沒有操作時,可以將耦合諧振器的頻率遠離量子位元的頻率,因為耦合強度反比於兩元件之間的頻率差(Detuning,失諧),此時兩個量子位元就可以視為隔離。

當需要進行閘運算時,再將頻率差縮小,就可以進行量子位元耦合。可調式設計可以兼顧製程後可調性,一方面可以透過訊號調整製程上的誤差;

另一方面還可實現可變QPU拓墣,即可以依照運算需求改變量子位元間的連結性。

Ref:Suppression of Qubit Crosstalk in a Tunable Coupling Superconducting Circuit

DOI: 10.1103/PhysRevApplied.12.054023

IBM走的不可調路線,可以大幅簡化電路設計的複雜度,較容易增加製程上量率,同時連外的線路少,接收到的雜訊也較少,IBM認為透過這種方式可以較快速實現量子優勢計算。

但同時也被迫面對量子位元因為直接耦合造成的串擾、一旦離開製程後就完全不可調整的缺點。

Google採幾乎全可調路線,就需要面對複雜的線路設計、更多的噪訊干擾等問題,也因為控制參數很多,需要大量的參數校正。

但全可調路線因為具有較高的彈性,可以透過外部儀器修正各項參數,可以逐步逼近最佳化,目前(2025)是Google領先,多數廠商也採用可調設計,連IBM也開始慢慢走向可調式設計。

▲能不能讓多個量子位元共用同一個耦合諧振器呢?目前也有相關的研究,這邊展示出10個量子位元共用同一個耦合器(B,Quantum Bus),也實現一種All-to-All connectivity。

具體可行的操作可以是耦合器的頻率遠離量子位元,當兩個量子位元要進行運算時,在將指定兩個量子位元的頻率移至與耦合器的頻率相近,運算完之後再移開頻率。

10-Qubit Entanglement and Parallel Logic Operations with a Superconducting Circuit

DOI: 10.1103/PhysRevLett.119.180511

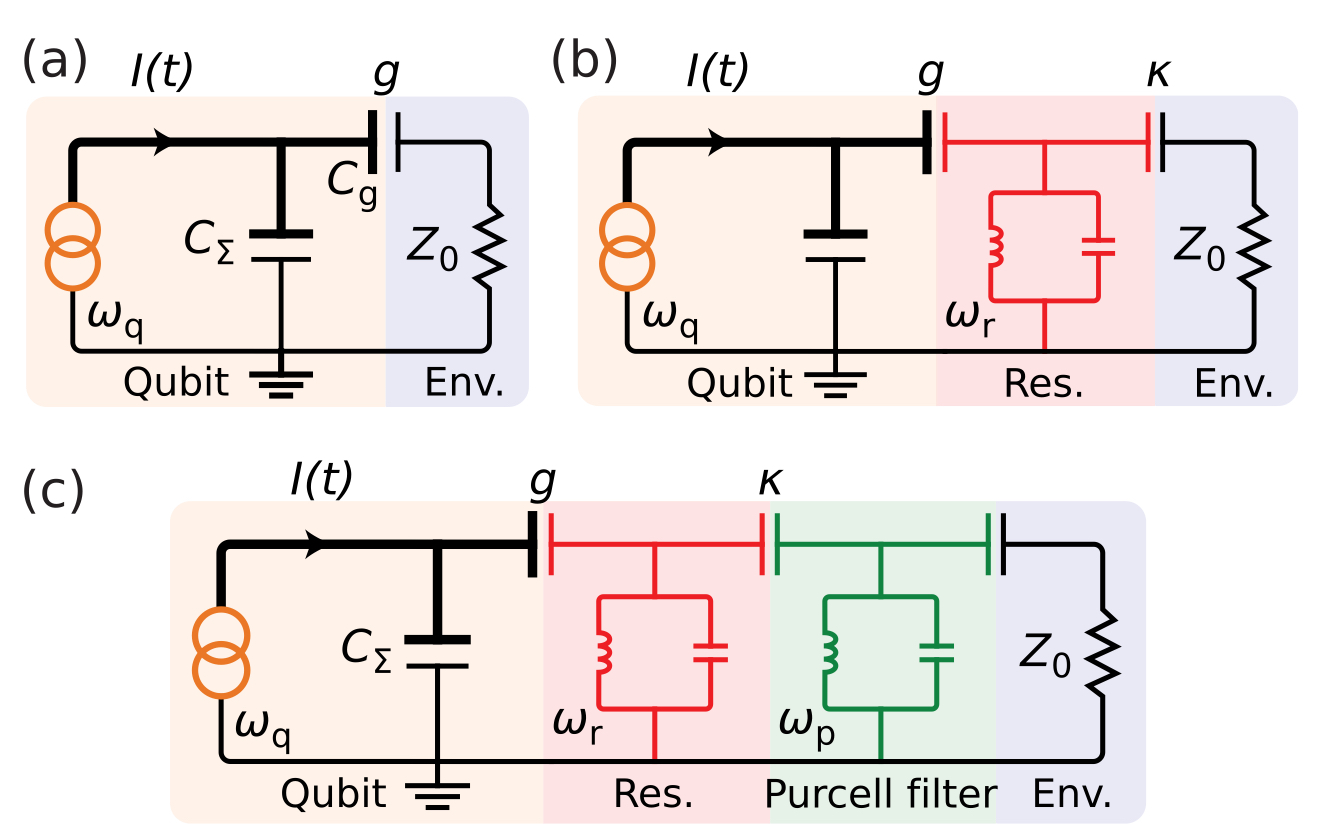

▲ 簡化來理解量子位元的讀取。

(a)早年採用直接讀取,外部電路直接量測量子位元。但這樣容易讓非預期的雜訊引入,也是一種破壞性量測。

(b)讓量子位元搭配一個耦合諧振器,藉由量測諧振器頻率的改變來間接得知量子位元的狀態,是一種QND量測,可以實現重複量測增加保真度。

(c)進一步搭配一個Purcell filter來增加保真度。Purcell filter的功用由下一張圖解說。

進一步瞭解超導量子位元的讀取,可以參考超導量子位元(進階版):量子計算硬體基礎

Ref: A quantum engineer's guide to superconducting qubits featuredFree

Doi: 10.1063/1.5089550

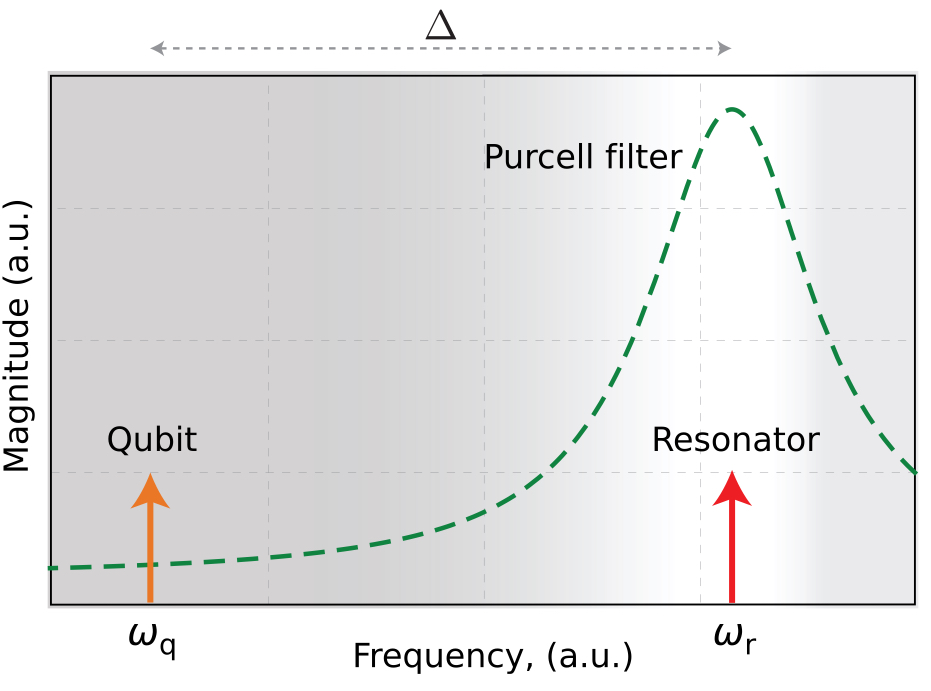

▲ Purcell Filter透波率對頻率的設計考量。雖然量子位元搭配一個耦合諧振器可以增加量測的保真度,

但量子位元的狀態還是有可能透過諧振器外流導致退相干。Purcell Filter透波率設計與諧振器的頻率對齊,可以保證良好的讀取信號輸入和輸出,

但是在量子位元自然頻率上壓制,確保量子位元的能量無法流出,提升相干時間。

Ref: A quantum engineer's guide to superconducting qubits featuredFree

Doi: 10.1063/1.5089550

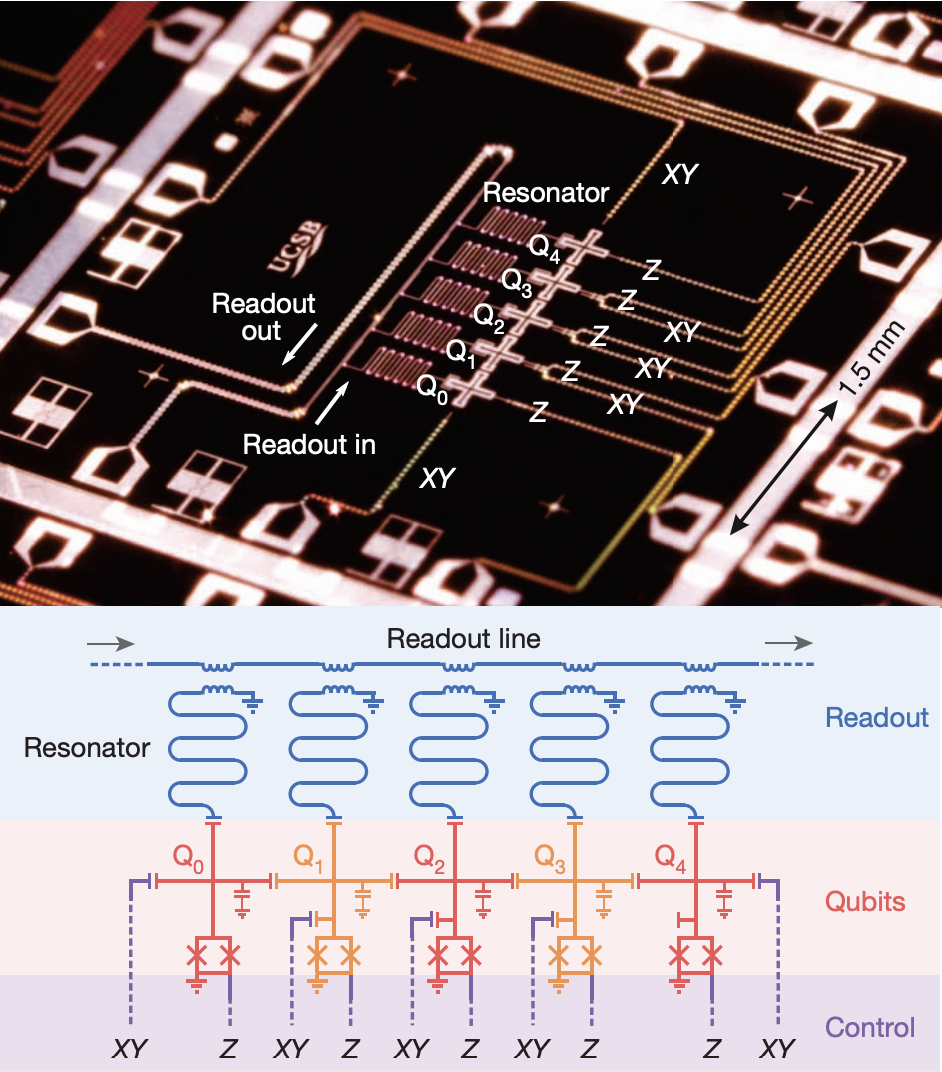

目前在量子位元晶片設計中,常常將個別量子位元的讀取共用同一條讀取線(Readout Bus or feedline),只要將每個讀取諧振器頻率錯開,就可以有效分析數據。 以下提供兩個範例:

▲這張是 5 qubit layout 的示意圖。其中 Z 是 flux line,XY 是 Drive line,5 個 Qubit 是直接電容耦合。此外,每個 qubit 都有自己的 readout resonator,在上方併入(此圖顯示是電感耦合)到 readout line。

doi.org/10.1038/nature13171

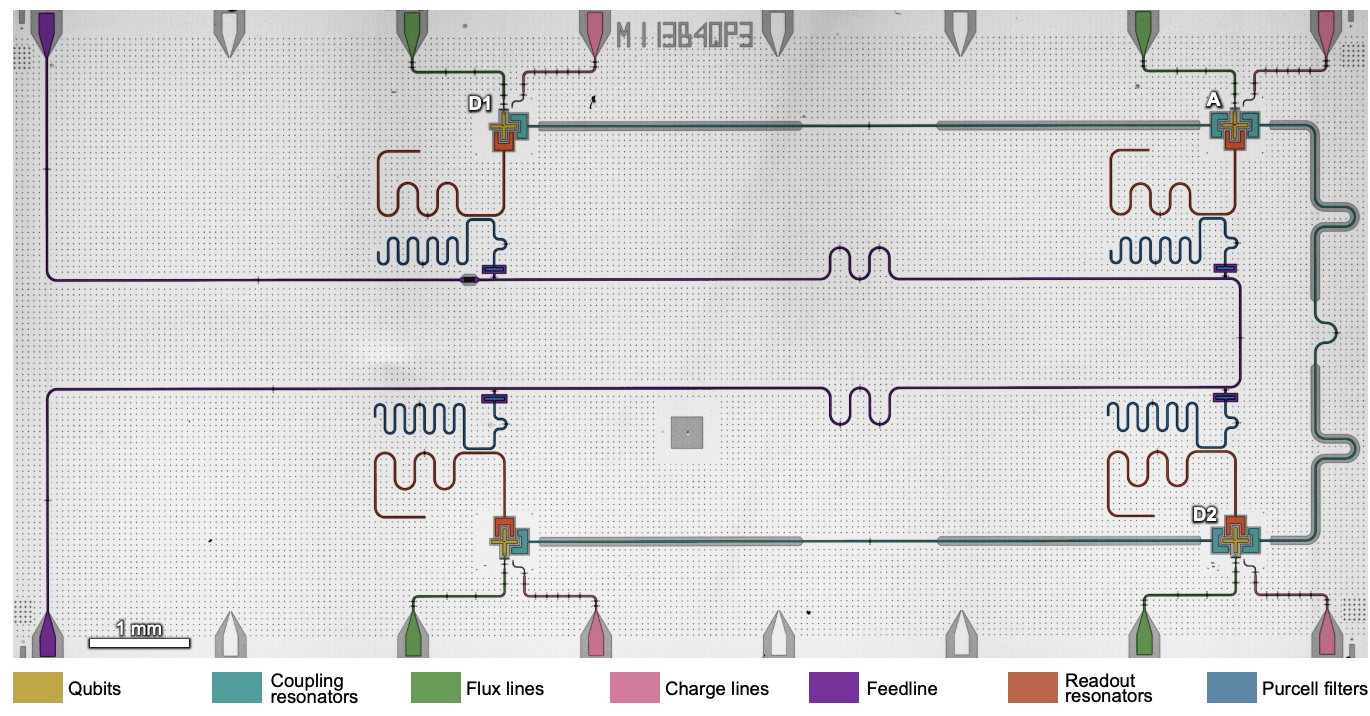

▲這張也是 5 qubit layout 的示意圖。圖中charge line表示XY control,量子位元間透過定頻率的耦合諧振器耦合。這邊可以與前一張圖比對,讀取諧振器跟總線間還有一個Purcell filter。

Entanglement stabilization using ancilla-based parity detection and real-time feedback in superconducting circuits

DOI: 10.1038/s41534-019-0185-4

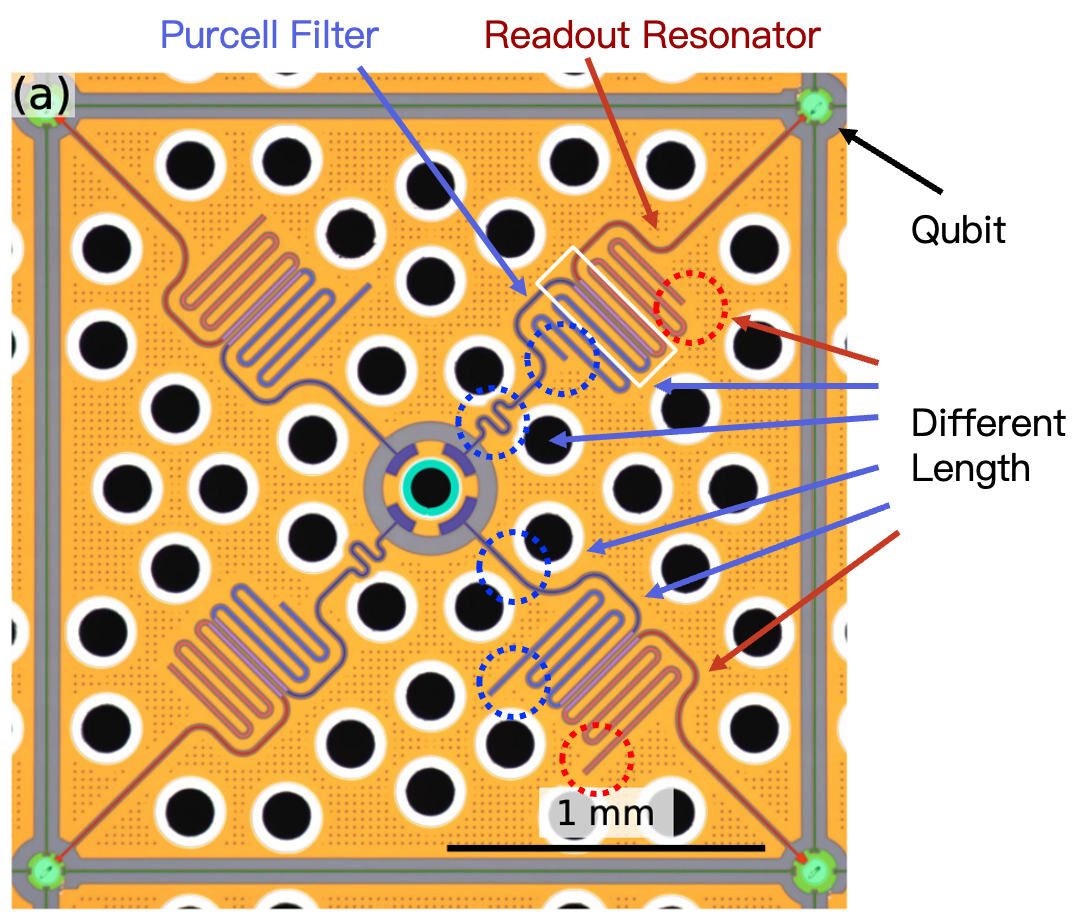

▲這張是 4 qubit layout 。圖正中間是讀取總線入口,連接四個Purcell filter和讀取諧振器,可以見到四個Purcell filter、讀取諧振器長度皆不相同,意味著不同的工作頻率。

Fast Multiplexed Superconducting-Qubit Readout with Intrinsic Purcell Filtering Using a Multiconductor Transmission Line

DOI: 10.1103/PRXQuantum.6.020345

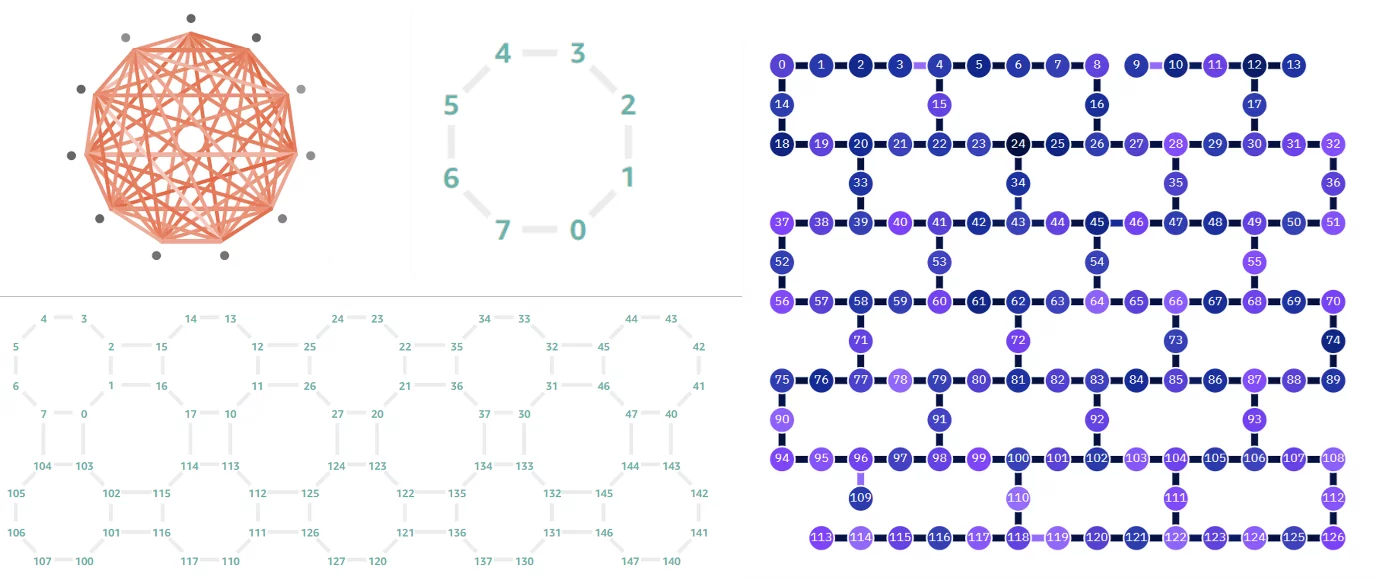

▲QPU拓墣表示量子位元間的連接性。要實現量子演算法優勢,盡可能實踐量子位元的All-to-All連接是重要的議題。然而對於固態量子位元體系(超導量子位元、半導體量子位元等) ,由於製程上的關係,多半是平面排列,這導致量子位元如果不採用3D線路連接,則只能跟鄰近的量子位元耦合。右圖為IBM目前的QPU拓墣。 而對於非固態量子位元體系如離子阱量子位元,可以透過離子的偶極交互作用實現遠程的耦合,從而實現All-to-All。

Ref: https://thequantuminsider.com/2022/08/12/a-guide-to-quantum-computing-benchmarking-and-certification/

Schematic representation of different QPU topologies. (Top-left: IonQ, Top-center: OXC, Bottom-left: Rigetti, Right: IBM). Images compiled from AWS Braket and IBM Quantum Experience sites.

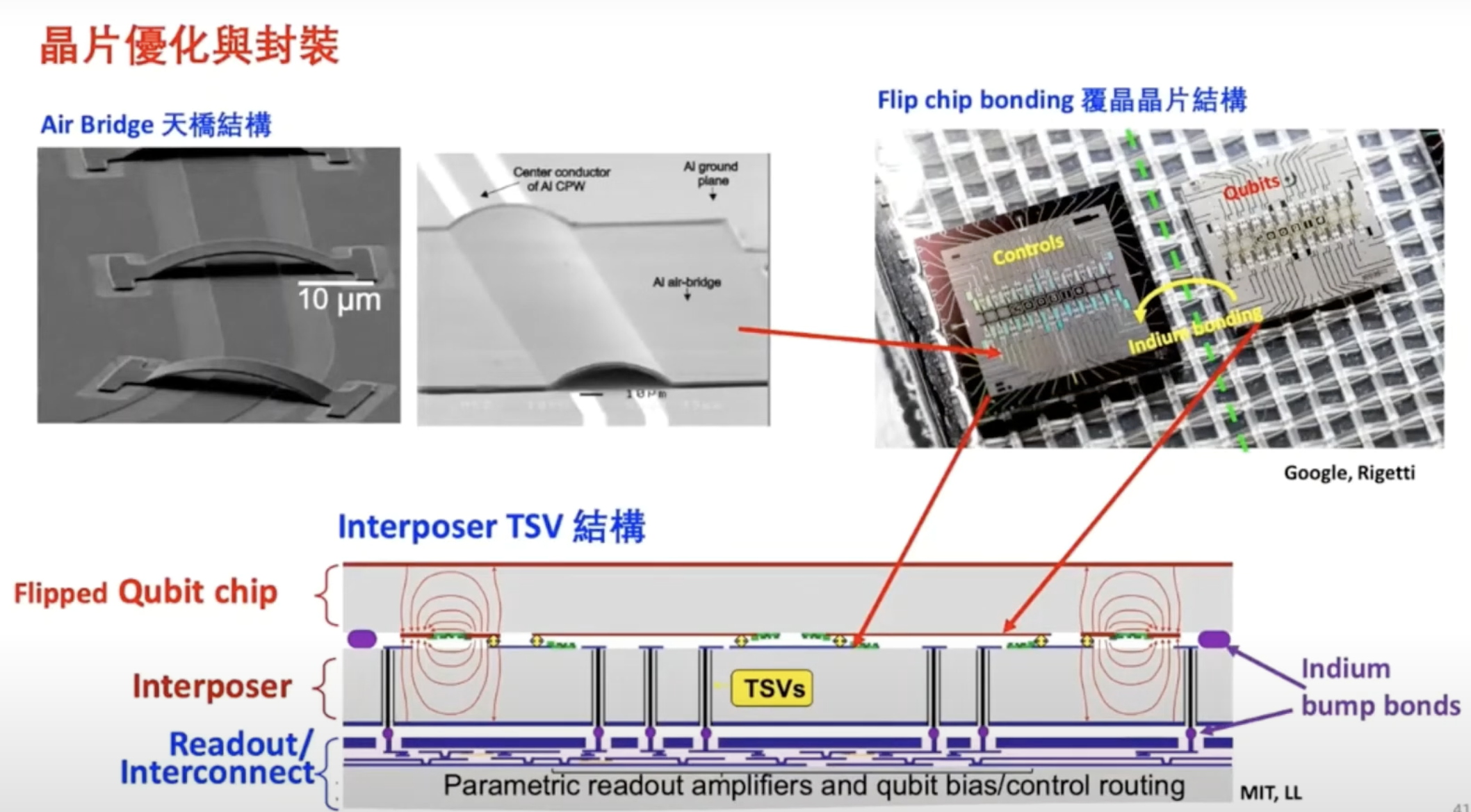

▲首先,固態量子位元體系多半是平面排列,各種控制線複雜的穿越導致線路之間勢必有跨越的問題。元件間的互相跨越(control line可以跨越resonator/coupler,但反之不宜)或是避免跨越(任何線路都不可跨越量子位元)

。再來,量子晶片亦需要在封裝上下功夫。當前主要採用覆晶封裝(flip chip),為了維持量子位元的保真度不受其他元件的干擾,

可以將量子晶片拆成兩層,需要高品質的區域放置量子位元,而其他如控制電路、讀取等線路放到另外一層,再將兩層疊在一起。

Ref: 如何打造一台量子電腦 (中央研究院物理研究所/陳啟東研究員) https://www.youtube.com/watch?v=wceckog180U&t=3420s

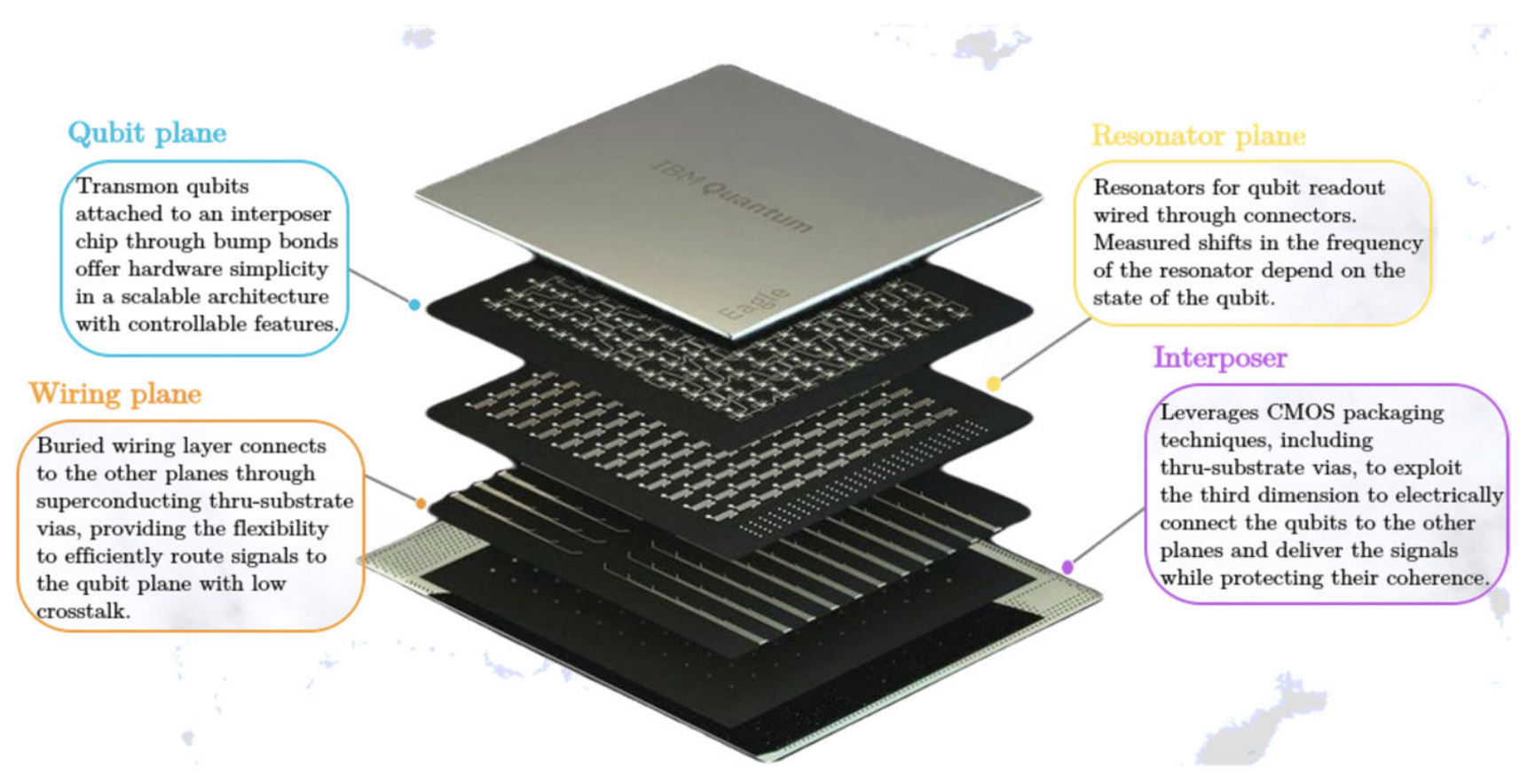

▲ 除了雙層的覆疊,目前也開始朝向將不同功能的元件分散到獨立的晶片曾。圖為IBM Eagle的設計,將量子位元、控制線路、諧振器分到不同的晶片層,減少干擾。

Ref: IBM quantum computers: evolution, performance, and future directions

DOI:10.1007/s11227-025-07047-7

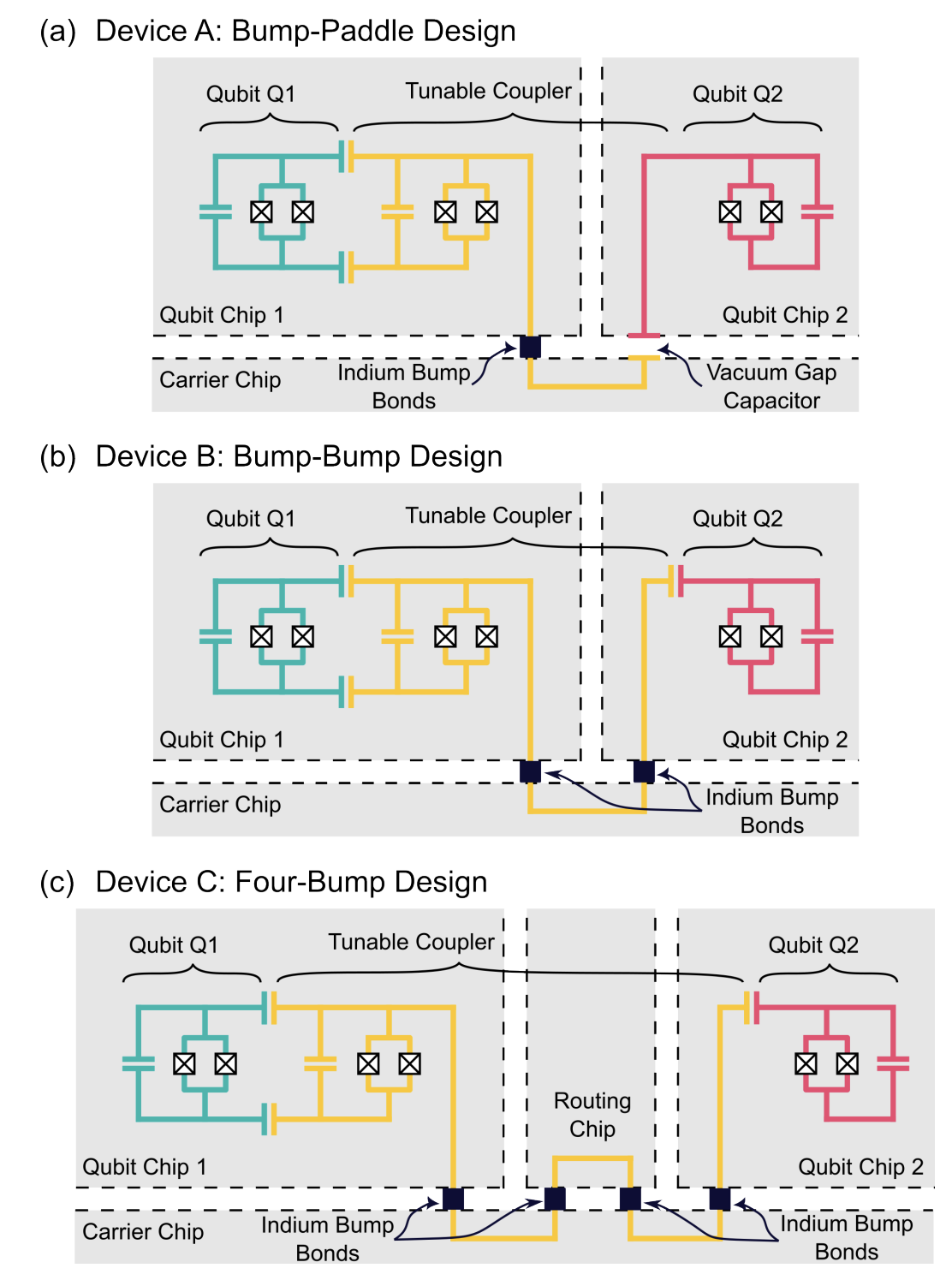

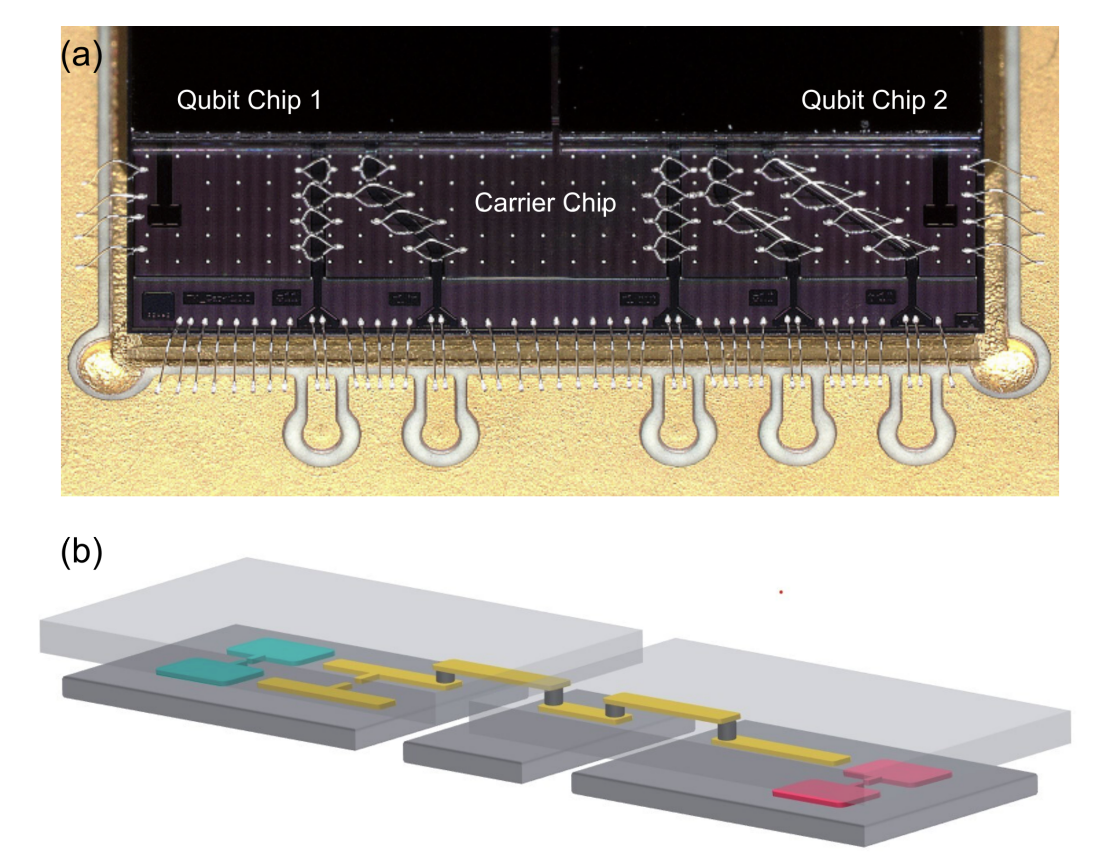

▲ 因為製程上的關係與超導量子位元的尺寸不小,除了將不同元件分在不同晶片上,

在單一晶片難以塞入大量的量子位元,故跨晶片的超導量子位元連結並保持量子特性亦是封裝上重要的實驗與挑戰。

Modular superconducting-qubit architecture with a multichip tunable coupler

DOI: 10.1103/PhysRevApplied.21.054063

串擾議題:古典串擾與量子串擾

在當前的量子電腦發展上,嚴格來說其實是半古典、半量子的綜合體,利用古典電腦發送帶有古典資訊的微波訊號,進入到量子位元後,

因為量子位元與微波耦合,會回傳帶有量子資訊的古典信號,再由古典電腦分析結果。

此特性可以稍微將串擾議題分類為古典串擾與量子串擾。

由控制訊號、閘操作造成的非預期影響,歸類為古典串擾;而量子串擾,來自於其他量子位元因為處在不同狀態,造成指定的量子位元控制不如預期。由下一節討論。

|

本文參考 由中興大學 郭華丞教授 應 中原大學 徐立義教授 邀請,主講題目:

Key issues in designing a scalable QPU

Event Date: 2025-06-18 Speaker: Prof. Watson Kuo (Dept. of Physics, National Chung Hsing University) Host: Prof. Li-Yi Hsu (CYCU) Place: R211, Science Building, Chung Yuan Christian University Time: 14:00 筆者深感啟發,特此致謝。 |

|---|

.png)

王培儒

王培儒