半導體自旋量子位元

引言

▲

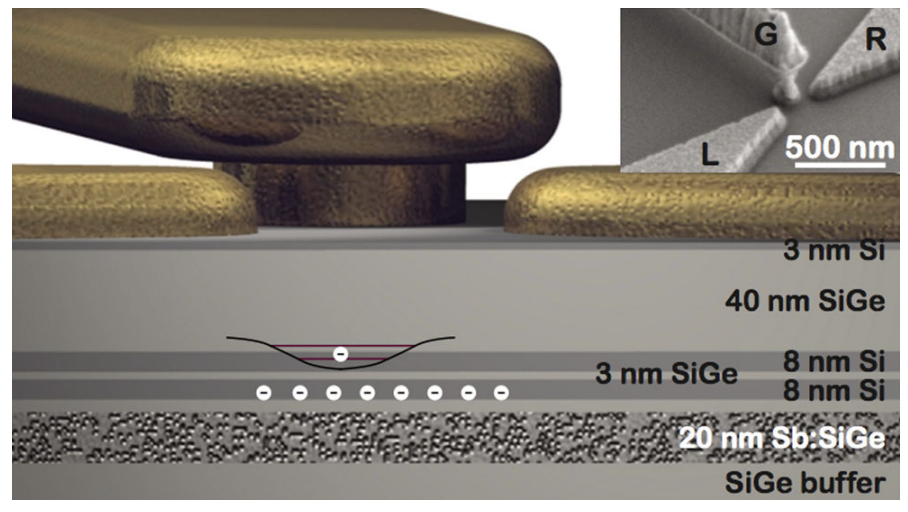

Silicon quantum electronics

DOI:10.1103/RevModPhys.85.961

▲

Ref: imec

https://www.imec-int.com/en/articles/moving-quantum-computing-lab-fab

▲

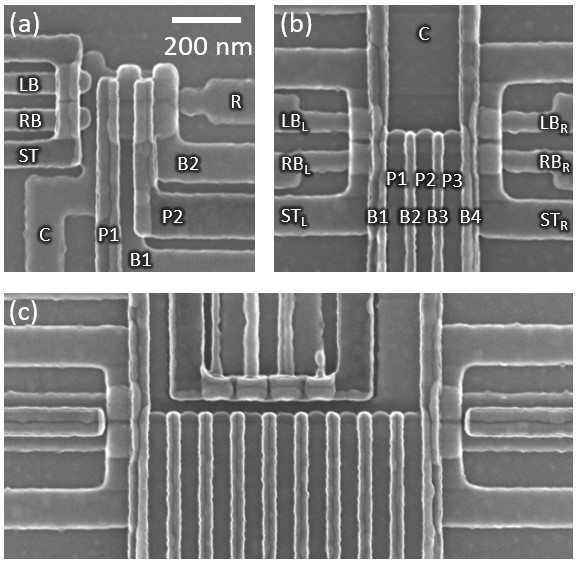

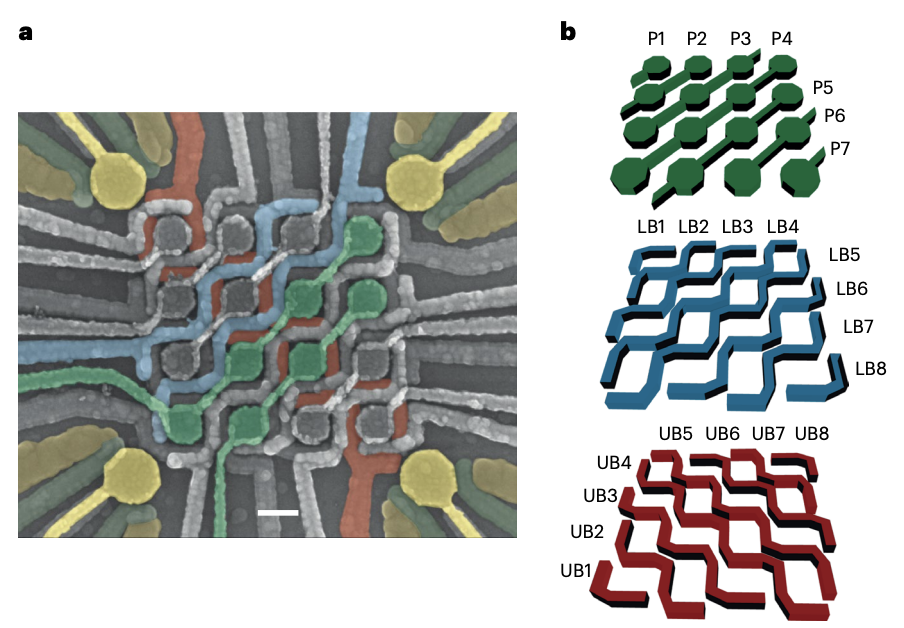

A tunable twodimensional crossbar array comprising 16 quantum dots

DOI: 10.1038/s41565-023-01491-3

半導體自旋量子位元:從基礎物理到可擴展量子計算之途

摘要

報告首先闡述了該技術的物理基礎,包括如何利用單一電子或電洞的自旋作為量子資訊的基本載體,以及如何透過奈米級的量子點結構(被譽為「人造原子」)來囚禁與操控這些自旋。接著,報告詳細剖析了實現量子運算所需的關鍵操作流程:從高保真度的量子態初始化、基於交換交互作用與自旋軌道耦合的普適量子邏輯閘操控,到利用泡利自旋封鎖與射頻反射技術進行的快速量子態讀取。

本報告的核心部分對三大主要半導體材料平台——矽(Si)、鍺(Ge)與砷化鎵(GaAs)——進行了嚴謹的比較分析。分析表明,儘管砷化鎵是該領域的開創性材料,但其固有的核自旋雜訊使其相干時間受限。相反地,矽,特別是經過同位素純化後的矽-28,提供了一個近乎完美的「自旋真空」環境,使得量子態的相干時間得以大幅延長,並在近年來實現了超過99.9%的單量子位元閘保真度與超過99%的雙量子位元閘保真度,達到了容錯計算的門檻。與此同時,以電洞自旋為基礎的鍺量子位元因其強大的內稟自旋軌道耦合,展現出全電控、高速操作的巨大潛力,成為備受矚目的新興方向。

報告進一步探討了實現大規模量子處理器所面臨的核心挑戰,包括元件的均勻性、量子位元間的連接性以及控制線路的「佈線瓶頸」。針對這些挑戰,報告闡述了前沿的解決方案,如用以克服連接限制的量子位元穿梭技術、旨在解決佈線難題的低溫CMOS(Cryo-CMOS)控制晶片整合,以及利用機器學習進行大規模自動化校準的策略。

第一章:半導體自旋量子位元的物理基礎

1.1 量子位元與自旋自由度

量子計算的基礎是量子位元(qubit),它是量子資訊的基本單位。與只能表示0或1的古典位元不同,量子位元是一個雙能階量子系統,可以同時處於其兩個基本狀態的疊加態 [1]。這兩個基本狀態通常被標記為 |0⟩ 和 |1⟩。在半導體自旋量子位元的物理實現中,這兩個邏輯狀態是透過單一基本粒子(通常是電子或電洞)的內在角動量——即「自旋」(spin)——來編碼的 [2, 3]。

自旋是粒子固有的量子力學屬性,其行為類似於一個微小的磁矩。當置於外部磁場中時,一個自旋為1/2的粒子(如電子)的自旋角動量會沿著磁場方向產生兩個可能的投影,即「自旋向上」(spin-up, |↑⟩)和「自旋向下」(spin-down, |↓⟩)。這兩個明確且正交的量子態天然地構成了量子位元的兩個基本狀態,即 |↑⟩ ≡ |1⟩ 和 |↓⟩ ≡ |0⟩ [3, 4]。

選擇自旋作為量子位元的載體具有一項根本性的優勢:自旋作為一個磁偶極矩,其與環境的交互作用主要是磁性的。相較於電荷,自旋對環境中的電場雜訊相對不敏感 [1]。在固態半導體環境中,電場雜訊(即電荷雜訊)是主要的退相干來源之一。因此,自旋的這種「內在惰性」使其能夠在嘈雜的固態環境中保持其量子態的疊加與糾纏特性更長的時間,這意味著潛在的長相干時間(coherence time),這是實現複雜量子計算的先決條件 [1]。這種相對的隔離性,使得電子自旋成為在固態系統中構建穩健量子位元的理想候選者。

1.2 量子點:固態系統中的「人造原子」

為了利用單一電子的自旋來承載量子資訊,首先必須將這個電子從半導體晶格中數以萬億計的其它電子中分離出來,並將其穩定地囚禁在一個極小的空間內。實現這一目標的關鍵技術是半導體量子點(Quantum Dot, QD)[2, 5]。

量子點是一種奈米級的半導體結構,其尺寸在三個維度上都小到足以對電子產生量子限制效應。在最常見的「閘極定義量子點」(gate-defined quantum dot)中,研究人員利用先進的微影技術,在半導體異質結構(如Si/SiO₂或Si/SiGe)的表面沉積一層複雜的奈米級金屬電極,稱為「閘極」(gates)[2, 6]。透過對這些閘極施加精確的負電壓,可以在其下方的半導體中產生一個靜電勢阱,將電子排斥開,從而形成一個微小的、孤立的電子島——這就是量子點 [5]。

這個被囚禁的電子由於空間受限,其能量不再是連續的,而是呈現出一系列分立的、類似原子能階的量子化能階。因此,量子點常被譽為「人造原子」(artificial atoms)[6, 7]。與真實原子不同的是,這些人造原子的性質,如尺寸、形狀以及其中囚禁的電子數目,都可以透過外部施加的閘極電壓進行精確地調控 [8]。

控制量子點中電子數目的核心物理原理是「庫侖阻塞」(Coulomb blockade)[5]。當一個電子進入量子點時,它會對後續進入的電子產生靜電排斥力。若要再加入一個電子,就必須提供足夠的能量來克服這個排斥力,這個能量被稱為「充電能」(charging energy)。透過精確調節閘極電壓,可以控制量子點的電化學勢,使其能夠逐一地裝載電子,從零個、一個、兩個,依此類推,直到可以精確地控制到只剩下最後一個電子 [2, 7]。這種對單一電荷的極致控制能力,是構建自旋量子位元的技術基石,它確保了我們可以擁有一個定義明確的、由單一自旋構成的量子位元。

第二章:量子位元的操作與量測

實現一個完整的量子計算流程,需要對量子位元進行一系列精確的時序操作,這包括將其設置到已知的初始狀態(初始化),對其進行邏輯運算(操控),以及在最後讀取其狀態(量測)。本章將深入探討這三個核心環節的物理原理和技術實現。

2.1 初始化:設定初始量子態

量子計算的可靠性始於一個確定性的起點。在演算法執行之前,系統中的所有量子位元都必須被精確地設置到一個共同的、已知的初始狀態,通常是計算基態|0⟩ [9]。對於單自旋量子位元,這對應於將電子自旋初始化為自旋向下|↓⟩的狀態。

一種常見的初始化方法是利用能量弛豫和電子隧穿 [16]。首先,在量子點附近設置一個電子儲存庫(reservoir),並在整個裝置上施加一個較強的靜態磁場。根據塞曼效應(Zeeman effect),這個磁場會使得電子的自旋向上|↑⟩和自旋向下|↓⟩兩個狀態的能量發生分裂,其中|↓⟩態的能量較低。接著,透過調控閘極電壓,將量子點的基態能階調整到略低於電子儲存庫的費米能階。在這種配置下,電子會從儲存庫隧穿進入量子點。一旦進入量子點,如果電子處於能量較高的|↑⟩態,它會透過與周圍環境(如晶格聲子)的能量交換,自發地弛豫(relax)到能量較低的|↓⟩態。等待一段時間(通常是幾個自旋弛豫時間$T_1$),就可以高機率地確保量子點中的電子處於|↓⟩態,從而完成初始化 [17]。

對於多電子編碼的量子位元,如S-T量子位元,初始化過程略有不同。例如,可以首先將兩個電子都置於同一個量子點中,形成電荷構型(0, 2)。在這種情況下,由於泡利不相容原理,兩個電子的基態必然是自旋單重態|S⟩。然後,透過快速的電壓脈衝將一個電子「拉」到相鄰的量子點,形成(1, 1)的電荷構型,同時保持其單重態的自旋特性。這樣,就將S-T量子位元初始化到了|S⟩態 [18]。

無論採用何種具體方法,高保真度的初始化都是後續所有量子操作的基礎。近年來的研究已經能夠實現超過99%的初始化保真度,為執行複雜的量子演算法和糾錯協議奠定了堅實的基礎 [19]。

2.2 操控:量子邏輯閘的物理實現

量子計算的核心在於執行一系列的量子邏輯閘,以操控量子位元的狀態並在它們之間建立糾纏。單量子位元閘對應於在布洛赫球(Bloch sphere)上對自旋狀態向量進行旋轉,而雙量子位元閘則用於實現量子位元之間的受控操作。在半導體自旋量子位元中,這些操作是透過精確控制兩種主要的物理機制來實現的:交換交互作用和自旋軌道耦合。

2.2.1 交換交互作用

交換交互作用是一種源自全同粒子(如電子)的量子統計特性和泡利不相容原理的純量子力學效應。當兩個囚禁在相鄰量子點中的電子的波函數發生重疊時,它們的總能量會根據其總自旋狀態(單重態或三重態)而發生分裂。這個能量差的大小就是交換交互作用的強度,通常用符號$J$表示 [4, 9]。

至關重要的是,$J$的大小對兩個量子點之間的靜電勢壘高度極為敏感。透過施加在兩個量子點之間的閘極上的電壓,研究人員可以精確地、快速地調控這個勢壘,從而實現對交換交互作用$J$的「開」與「關」,其強度可以被調控數個數量級 [4]。當$J$開啟時,它會在單重態|S⟩和三重態|T₀⟩之間驅動一個相干的振盪。這種全電控的機制是實現快速雙量子位元閘的理想方式。例如,透過精確控制$J$開啟的時間,可以實現$\sqrt{\text{SWAP}}$閘或受控相位(CPHASE)閘,這些都是構建通用量子計算機所需的基礎糾纏閘 [6, 20]。

實現高保真度的交換閘(如SWAP閘)的一個關鍵挑戰是需要滿足$J \gg \Delta E_z$的條件,其中$\Delta E_z$是兩個量子位元之間的塞曼能量差 [20]。在實際裝置中,由於微磁體或材料本身的不均勻性,$\Delta E_z$往往不為零。如何在大範圍內獨立調控$J$和$\Delta E_z$以優化其比率,是當前研究的一個重點。最近的研究表明,利用自旋軌道耦合效應,可以在調控$J$的同時反向調節$\Delta E_z$,從而實現了對$J/\Delta E_z$比值超過兩個數量級的調控,為高保真度SWAP閘的實現鋪平了道路 [20]。

2.2.2 自旋軌道耦合與電驅動Rabi振盪

單量子位元閘,即對單個自旋進行任意角度的旋轉,是透過驅動「拉比振盪」(Rabi oscillations)來實現的。拉比振盪是指在一個共振的交變場驅動下,一個雙能階系統在其兩個本徵態之間進行週期性躍遷的現象 [21]。對於自旋量子位元,這意味著施加一個頻率等於自旋能階分裂(塞曼能量)的振盪場,使自旋在|↑⟩和|↓⟩之間來回翻轉。透過精確控制這個振盪場的持續時間,就可以實現任意角度的旋轉 [21]。

雖然這個振盪場可以是磁場(即電子自旋共振,ESR),但一個更具可擴展性的方法是利用電場來驅動,這被稱為「電偶極自旋共振」(Electric Dipole Spin Resonance, EDSR)[21]。電場本身不直接與電子的自旋耦合,但它可以透過「自旋軌道耦合」(Spin-Orbit Coupling, SOC)這一媒介來間接影響自旋 [22]。SOC是固體材料中一種相對論效應,它將電子的自旋與其在晶格中的運動(軌道角動量)聯繫起來。

在EDSR方案中,一個交流電場(可由閘極施加的微波脈衝產生)會週期性地驅動電子在量子點內來回運動。由於SOC的存在,電子的這種運動會讓它感受到一個等效的、與其運動方向和自旋相關的有效磁場。這個有效磁場也是振盪的,並且如果其頻率與量子位元的共振頻率匹配,就能夠驅動拉比振盪,實現對自旋的電學操控 [21]。EDSR的優勢在於,電場比磁場更容易在奈米尺度上被局域化,從而可以對陣列中的單個量子位元進行精確的定址操作,減少串擾(crosstalk)。

這兩種操控機制——交換交互作用和自旋軌道耦合——的選擇和優化,構成了半導體自旋量子位元架構設計的核心。雙量子位元閘主要依賴交換作用,這要求量子點之間的耦合是可控且足夠強的。而全電控的單量子位元閘則依賴SOC。這就引出了一個關鍵的材料科學問題:不同半導體材料的SOC強度差異巨大。例如,砷化鎵(GaAs)和鍺(Ge)擁有較強的內稟SOC,這使得在這些材料中實現快速的EDSR相對容易 [23]。相比之下,矽(Si)的內稟SOC非常弱。為了在矽中實現高效的電學操控,研究人員必須「人工設計」出一個有效的SOC機制,常見的方法是在量子點附近集成一個微磁體(micromagnet)。這個微磁體會產生一個強烈的、不均勻的靜磁場梯度。當電場驅動電子在這個梯度磁場中運動時,電子會感受到一個位置依賴的塞曼能量變化,這等效於一種人造的SOC,從而能夠實現EDSR [6, 18, 20]。

因此,材料的選擇與器件的設計之間存在著深刻的權衡。選擇強SOC材料(如Ge)可以簡化單量子位元閘的設計,但強SOC也可能成為一個額外的雜訊通道,使自旋更容易受到電荷雜訊的影響。選擇弱SOC材料(如Si)可以獲得更長的內稟相干時間,但需要引入額外的元件(如微磁體)來實現有效的電學操控,增加了製造的複雜性。理想的系統應當能夠對交換作用和SOC(或等效機制)進行獨立且精確的調控,這正是當前材料工程與器件物理研究的前沿方向。

2.3 讀取:將自旋資訊轉換為可測量訊號

在量子計算的最後一步,必須測量每個量子位元的最終狀態以獲取結果。直接測量單個電子的自旋磁矩極其困難。因此,在半導體自旋量子位元中,讀取過程通常依賴於一種間接的測量方案,即首先將難以測量的「自旋資訊」巧妙地轉換為易於測量的「電荷資訊」,這個過程被稱為「自旋-電荷轉換」(spin-to-charge conversion)。

2.3.1 泡利自旋封鎖原理

目前最廣泛使用的讀取機制是基於「泡利自旋封鎖」(Pauli Spin Blockade, PSB)的原理 [14, 24]。PSB是一種發生在雙量子點(DQD)系統中的輸運現象,其核心思想是利用泡利不相容原理來區分不同的雙電子自旋態 [25]。

PSB的典型設置如下:一個DQD被耦合到源極(source)和汲極(drain)兩個電子儲存庫之間,並施加一個偏壓,驅動電子從源極流向汲極。電子隧穿的路徑被設計為必須經過一個(1, 1) → (0, 2)的電荷轉移過程,即一個電子從左點隧穿到右點,與右點原有的電子形成雙電子佔據狀態 [24]。這裡的(n, m)表示左、右量子點中的電子數。

這個過程的關鍵在於,(0, 2)狀態的基態是一個自旋單重態|S⟩。根據泡利不相容原理,兩個自旋相同的電子(如|↑↑⟩或|↓↓⟩)不能佔據同一個軌道基態。因此:

- 如果(1, 1)態的兩個電子處於單重態

|S⟩,它們的總自旋相反。當它們嘗試形成(0, 2)態時,可以直接躍遷到(0, 2)的單重態基態。這個過程是允許的,電子可以順利流過DQD,產生一個可測量的電流 [14, 21]。

- 如果(1, 1)態的兩個電子處于三重態(如

|T+⟩ = |↑↑⟩),它們的自旋平行。由於泡利不相容原理,它們無法直接形成(0, 2)的單重態基態。如果(0, 2)的三重態能階遠高於(1, 1)態的能階,那麼這個隧穿過程就被能量守恆和泡利原理共同「阻塞」了。因此,電流被阻斷 [21, 24]。

通過測量流經DQD的電流是否存在,就可以推斷出(1, 1)態的自旋是單重態(有電流)還是三重態(無電流)。這就成功地將不可直接測量的自旋資訊轉換成了可以透過標準電流計輕鬆測量的電荷(電流)資訊 [26]。在某些特定的磁場和系統參數下,也可能出現所謂的「奇偶讀取」(parity readout),即只有自旋平行的|T+⟩和|T-⟩態被阻塞,而|T₀⟩態可以快速弛豫到|S⟩態從而解除阻塞。這種讀取方式可以區分自旋的奇偶性(平行或反平行)[27]。

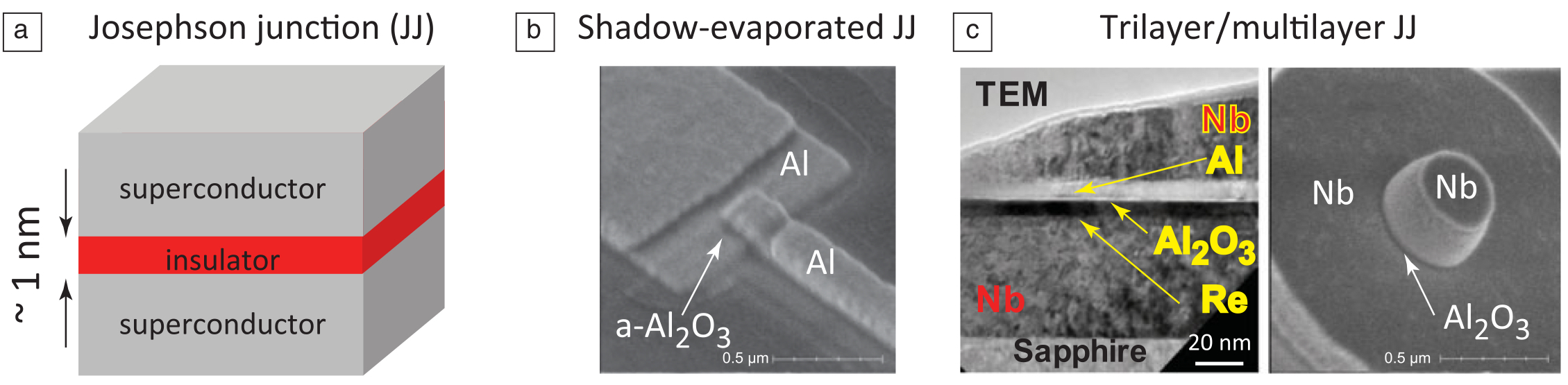

2.3.2 色散式讀取與射頻反射技術

儘管PSB是一種非常有效的讀取方法,但它依賴於電荷的實際隧穿,這個過程本身可能會對量子態造成擾動,並且速度受到隧穿速率的限制。一種更先進、更快速且侵擾性更低的讀取技術是「色散式讀取」(dispersive readout),通常與「射頻反射技術」(RF-reflectometry)相結合 [13, 28]。

在這種方案中,其中一個量子點的控制閘極被集成到一個高頻LC諧振電路(也稱為「tank circuit」)中。這個電路的諧振頻率對其總電容非常敏感。當DQD系統處於電荷轉移的邊界時(例如(1, 1)和(0, 2)態能量簡併的點),系統會表現出一個額外的「量子電容」。重要的是,這個量子電容的大小取決於所涉及的自旋態(單重態或三重態)[28]。

因此,自旋態的不同會導致諧振電路總電容的微小變化,進而使其諧振頻率發生一個微小的「色散頻移」(dispersive shift)。透過向這個諧振電路發送一個頻率接近其諧振頻率的射頻(RF)探測信號,並測量反射信號的振幅和相位,就可以精確地探測到這個頻移。單重態和三重態會對應不同的反射信號,從而實現對自旋態的區分 [13, 28]。

色散式讀取的主要優點是速度快(可達奈秒級)和高保真度,因為它不需要電子實際隧穿離開量子點,是一種更為「量子非破壞性」(Quantum Non-Demolition, QND)的測量方式。這種方法已經在超導量子位元中被廣泛應用,並成功地應用於半導體自旋量子位元,成為實現快速、高保真度單次讀取(single-shot readout)的主流技術之一 [13, 29]。

第四章:性能指標與前沿進展

評估一個量子計算平台的優劣,主要依賴於一系列可量化的關鍵性能指標(metrics),其中最核心的是相干時間和操作保真度。這些指標直接決定了量子計算機能夠執行多麼複雜的演算法以及其結果的可靠性。本章將深入探討這些指標的定義、當前的世界紀錄,以及影響這些指標的雜訊來源和相應的抑制策略。

4.1 相干時間:量子態的壽命

相干時間是衡量一個量子位元能夠維持其脆弱的量子疊加態和糾纏態而不被環境破壞的時間長度。它通常由兩個特徵時間來描述:

- 縱向弛豫時間 ($T_1$): 也稱為能量弛豫時間,它描述了量子位元從高能態

|1⟩自發衰減到低能態|0⟩的平均時間。$T_1$為量子計算設定了絕對的時間上限。在同位素純化的矽中,由於自旋與晶格的耦合非常弱,$T_1$可以達到驚人的長度,實驗中已觀測到數秒甚至更長的時間 [34, 35]。

- 橫向退相干時間 ($T_2$): 也稱為相位退相干時間,它描述了量子位元疊加態的相對相位關係因環境雜訊而逐漸模糊的過程。$T_2$通常比$T_1$短得多,是限制量子計算複雜度的更主要因素。$T_2$有幾種不同的測量定義:

- $T_2^*$ (Ramsey退相干時間): 這是最基本的相干時間測量,它反映了量子位元在自由演化時受到所有(包括緩慢變化的準靜態雜訊)影響下的退相干速率。在高品質的28Si/SiGe器件中,$T_2^*$已達到數十微秒的水平,例如30.4 µs [35]。

- $T_2^{\text{Hahn}}$ (Hahn回波退相干時間): 透過施加一個簡單的$\pi$脈衝(自旋回波),可以消除準靜態和低頻雜訊的影響,從而顯著延長相干時間。在同位素純化矽中,$T_2^{\text{Hahn}}$可以達到數百微秒甚至毫秒級別,例如803 µs [34, 35]。

近年來,透過更先進的「動力學解耦」(Dynamical Decoupling)序列,如連續波解耦(Continuous-Wave Concatenated Decoupling, CCD),研究人員能夠更有效地抑制環境雜訊,將一個天然矽(非純化)量子位元的$T_2^*$從143 ns大幅提升至40.7 µs,展示了主動雜訊抑制技術的強大威力 [31, 32]。對於新興的鍺平台,Ge/Si奈米線中的電洞自旋量子位元已展示出130 ns的$T_2^*$ [37],而金剛石中的鍺空位色心(一種不同的固態自旋系統)的相干時間甚至達到了毫秒級 [38],顯示了鍺基材料的巨大潛力。

4.2 保真度:量子操作的精確度

保真度(Fidelity)是衡量一次量子操作(如初始化、閘操作或讀取)的實際結果與其理想的、理論上的結果之間接近程度的指標。對於需要數百萬甚至數十億次連續操作的容錯量子計算而言,單次操作的保真度必須極高,通常要求達到99.9%以上(即錯誤率低於0.1%)。

4.2.1 單量子位元閘保真度紀錄

單量子位元閘的保真度是衡量對單個自旋進行精確旋轉控制能力的核心指標。得益於同位素純化矽提供的低雜訊環境以及控制技術的進步,矽自旋量子位元的單量子位元閘保真度在近年來取得了突破性進展。多個研究團隊已經報導了超過99.9%的單量子位元閘保真度,成功跨越了容錯計算的關鍵閾值 [6, 19]。更令人鼓舞的是,即使在未經同位素純化的天然矽器件中,透過採用先進的雜訊抑制和脈衝整形技術,單量子位元閘保真度也已能穩定地超過99% [39, 40],這大大降低了對昂貴的同位素純化材料的依賴,為商業化應用開闢了更廣闊的道路。

4.2.2 雙量子位元閘的挑戰與突破

雙量子位元閘,即在兩個量子位元之間產生糾纏的邏輯門,其實現比單量子位元閘更具挑戰性。因為它不僅需要對單個自旋進行精確控制,還需要對它們之間的交互作用(通常是交換交互作用$J$)進行精確的時序控制,並且更容易受到串擾和電荷雜訊的影響。在很長一段時間裡,雙量子位元閘的保真度是矽自旋量子位元平台的一大短板,遠落後於超導量子位元等競爭對手。

然而,過去幾年見證了這一領域的巨大突破。透過對器件設計的優化、材料質量的提升以及對交換交互作用脈衝的精確校準,多個頂尖研究團隊相繼報導了超過99%的雙量子位元閘保真度 [1, 19]。其中一項里程碑式的工作,在一個Si/SiGe雙量子位元處理器上,實現了高達99.8%的受控相位(CPHASE)閘保真度 [19]。

最為關鍵的進展來自於2024至2025年間的研究報告,一個由學術界和工業界合作的團隊,首次在一個完全由工業級300mm CMOS晶圓廠製造的矽量子晶片上,系統性地驗證了其性能。利用門組斷層掃描(Gate Set Tomography, GST)這一嚴格的基準測試工具,他們證明了該晶片上所有的單量子位元和雙量子位元操作的保真度均穩定超過99%,同時態製備和測量(SPAM)的保真度也超過了99.9% [34, 35]。這一成就的意義不僅在於達到了高保真度,更在於證明了這種高性能是可以在標準化、大規模的工業製造流程中實現的,這是從實驗室「英雄器件」走向可商業化量子處理器的決定性一步。

4.3 雜訊來源與抑制策略

實現高相干性和高保真度的核心,在於理解並抑制各種來源的雜訊。在半導體自旋量子位元中,主要的雜訊來源包括:

- 電荷雜訊 (Charge Noise): 這是指半導體襯底、界面或附近缺陷中俘獲的電荷發生隨機波動,從而產生一個隨機起伏的電場 [10]。這個隨機電場會透過斯塔克效應(Stark effect)微擾量子點的能級,或者更顯著地,透過自旋軌道耦合機制轉化為對自旋的有效磁雜訊,導致相位退相干 [4, 32]。電荷雜訊是限制當前高品質矽器件(特別是Si-MOS結構)性能的主要瓶頸之一。

- 核自旋雜訊 (Nuclear Spin Noise): 如前所述,這是由宿主材料中非零核自旋透過超精細交互作用產生的磁雜訊。它是GaAs和天然矽中退相干的主要來源,但在同位素純化的28Si中可以被有效抑制 [3, 30, 39]。

為了對抗這些雜訊,研究人員發展了多種抑制策略,這些策略可以大致分為被動和主動兩類:

- 被動抑制: 主要從材料和器件設計入手。最成功的例子就是採用同位素純化的28Si來消除核自旋雜訊 [1]。選擇電荷雜訊更低的Si/SiGe異質結構,或者透過優化Si-MOS的製造工藝來改善界面質量,也是重要的被動抑制手段。此外,研究人員還可以透過精確調節閘極電壓,將量子位元操作在特定的「甜蜜點」(sweet spots)。在這些點上,量子位元的能階對電場的一階變化不敏感,從而可以有效抑制電荷雜訊的影響 [36]。

- 主動抑制 (動力學解耦): 這是一種更為主動的策略,其思想類似於降噪耳機。它透過對量子位元施加一系列精心設計的控制脈衝序列,來主動地「重聚焦」量子位元的相位,從而抵消緩慢變化的環境雜訊的影響。最簡單的動力學解耦序列是Hahn回波,而更複雜的序列,如CPMG或前面提到的CCD序列,可以更有效地抑制更寬頻譜的雜訊,從而顯著延長相干時間 [31, 32, 41, 42]。

該領域的發展趨勢清晰地表明,雜訊抑制策略正在從單一的材料科學問題,演變為一個複雜的量子控制工程問題。在早期的GaAs研究中,首要任務是戰勝超精細交互作用這個「巨獸」。當透過轉向純化矽解決了這個問題後,一直被掩蓋的電荷雜訊問題便凸顯出來,成為新的主要矛盾。在當今最先進的器件中,研究人員需要同時應對殘餘的電荷雜訊、來自控制電路的高頻熱雜訊,以及量子位元之間的串擾等多種雜訊源。這解釋了為何控制策略變得日益複雜和精妙,從簡單的材料選擇,發展到結合了脈衝整形、動力學解耦和基於機器學習的自動化校準等多種手段的綜合性解決方案 [43, 44]。這標誌著該領域在邁向實用化的道路上,正從物理原理的驗證階段,深入到系統工程的精細調控階段。

第五章:可擴展性之路:架構、連接與整合

半導體自旋量子位元最核心的承諾是其無與倫比的可擴展性潛力。然而,要將數百萬甚至數十億個量子位元集成到單一晶片上,遠非簡單地複製單個量子位元那麼簡單。它帶來了一系列系統級的工程挑戰,主要集中在量子處理器的架構設計、量子位元之間的連接性,以及量子與古典控制電路的整合。本章將探討應對這些挑戰的前沿方案。

5.1 從線性陣列到二維結構

早期的自旋量子位元器件通常採用一維的線性陣列結構,即幾個量子點沿直線排列 [19, 45]。這種結構相對簡單,易於製造和控制,足以用來驗證基本的量子閘操作和小型演算法。然而,要實現真正有用的、能夠抵禦錯誤的容錯量子計算,僅有一維結構是遠遠不夠的。

當前最主流的量子糾錯碼(Quantum Error Correction, QEC)方案,如「表面碼」(surface code),要求量子位元被佈置在一個二維(2D)的網格上,並且每個數據量子位元都需要與其最近的四個鄰居(測量量子位元)進行交互 [18, 46]。因此,從一維線性陣列走向二維網格架構,是實現可擴展量子計算的必經之路。

然而,構建一個密集的二維量子點陣列面臨著巨大的挑戰,其中最突出的是「佈線瓶頸」(wiring bottleneck)或「扇出問題」(fan-out problem)[10]。在二維陣列中,每個量子點都需要多個獨立的閘極來進行囚禁和操控。隨著量子位元數量的增加,這些控制線路需要從晶片邊緣延伸到陣列中心,它們會佔據大量空間,並且彼此之間的交叉和佈局變得極其複雜和密集。這不僅增加了製造的難度,還可能引入嚴重的電磁串擾,影響量子位元的性能 [6]。學術界已經提出了多種二維陣列的設計方案,例如3x3的量子點陣列,但如何有效解決佈線問題,是實現更大規模二維處理器的關鍵障礙 [18]。

5.2 克服連接瓶頸:量子位元穿梭技術

為了解決二維陣列中的連接性問題,研究人員提出了一種極具創造性的方案——「量子位元穿梭」(qubit shuttling)[41, 47]。其核心思想是,與其為每一對需要交互的量子位元都建立一條固定的物理連接(這在大型陣列中是不現實的),不如讓量子位元本身「動起來」。

在量子位元穿梭技術中,承載量子資訊的單個電子,可以透過對一排閘極施加一系列精確計時的電壓脈衝,被穩定地從一個量子點傳送到另一個量子點,就像在一個「電子傳輸帶」上移動一樣 [47]。這種動態的重新配置能力徹底改變了量子處理器的架構範式。它意味著:

- 解決遠距離連接: 一個量子位元可以被「穿梭」到晶片的任何一個角落,與另一個遙遠的量子位元進行交互,從而實現了有效的遠距離連接,打破了最近鄰交互的限制 [41]。

- 優化資源利用: 可以設計專門的功能區,例如,將量子位元穿梭到一個專門的「計算區」進行多量子位元閘操作,然後再將其穿梭到一個高度優化的「讀取區」進行高保真度測量,從而提高了整個晶片的資源利用效率。

- 簡化架構設計: 穿梭技術大大緩解了對密集物理佈線的需求,為控制電路和其他元件留出了寶貴的晶片空間,從而簡化了大規模陣列的設計 [41]。

量子位元穿梭的關鍵挑戰在於,必須在移動過程中保持電子自旋態的相干性。令人振奮的是,近期的實驗已經取得了重大突破。在同位素純化的矽中,研究人員展示了在200奈秒內將電子穿梭10微米遠的距離,其平均保真度高達99.5% [47]。更值得注意的是,在具有強自旋軌道耦合的鍺中,穿梭技術同樣被證明是可行的。研究表明,強大的SOC雖然會讓移動中的自旋快速旋轉,但這種旋轉是確定性的、可控的,其本身就像一種內在的動力學解耦,反而有助於抑制隨機的電荷雜訊,從而實現了相干穿梭 [41, 48, 49]。這些成果表明,量子位元穿梭是構建可擴展半導體量子處理器的一項極具前景的關鍵使能技術。

5.3 解決佈線難題:低溫CMOS (Cryo-CMOS) 控制電路

即使有了量子位元穿梭技術,當量子位元的數量達到數百萬時,從室溫的控制儀器連接到在極低溫(通常在1K以下)環境中工作的量子晶片的線纜數量,仍然是一個無法逾越的物理障礙。每增加一個控制信號,就需要一根從室溫延伸到低溫區的同軸電纜,這不僅會佔用巨大的物理空間,更重要的是,每根線纜都會將室溫的熱量傳導到稀釋製冷機的冷端,最終會超出製冷機的冷卻能力 [50, 51]。

解決這一終極佈線瓶頸的方案,是將傳統上位於室溫的龐大古典控制電子設備,微縮到一個或幾個專門設計的CMOS晶片上,並將這些控制晶片與量子晶片一同放置在低溫環境中,實現「片上系統」(System-on-Chip)或「多晶片模組」(Multi-Chip Module)的集成。這種能夠在極低溫(通常是4K或更低)下工作的CMOS電路,被稱為「低溫CMOS」(Cryogenic CMOS, Cryo-CMOS)[52]。

Cryo-CMOS技術的目標是將量子位元的控制和讀取功能,如產生精確的微波脈衝、施加閘極電壓、以及放大微弱的讀取信號等,全部集成到一個緊鄰量子處理器的古典晶片上 [51, 52]。這樣做的好處是革命性的:

- 它將離開製冷機的數百萬根線纜,簡化為少數幾根用於供電和高速數據傳輸的數字線纜,徹底解決了佈線瓶頸 [53]。

- 它縮短了控制信號的傳輸路徑,減少了延遲和信號失真,有利於實現更快速、更精確的量子位元控制和反饋操作。

- 它為構建模組化、可擴展的量子計算機系統鋪平了道路。

開發Cryo-CMOS面臨的主要挑戰是,標準的CMOS電晶體並非為在極低溫下工作而設計,其性能會發生顯著變化。此外,控制晶片本身在工作時會產生熱量,必須將其功耗控制在極低的水平(微瓦級),以免加熱量子位元,破壞其脆弱的量子態。全球範圍內,包括英特爾、Diraq的合作夥伴Emergence Quantum,以及台灣的國家級研究計畫,都在大力投入研發超低功耗的Cryo-CMOS技術,例如開發專用的低溫電晶體、多路復用器(multiplexer)和數位類比轉換器(DAC),這被視為實現大規模量子計算的關鍵瓶頸技術之一 [53, 54, 55, 56]。

5.4 元件均勻性與良率的挑戰

從製造一個「英雄」器件到量產數百萬個性能一致的量子位元,最大的鴻溝之一在於「元件的均勻性」(device uniformity)[10]。量子點的物理和電學特性,如其尺寸、形狀、能級結構和與鄰居的耦合強度,對其奈米級的幾何形狀和局域靜電環境極其敏感。在目前的製造工藝中,即使是在同一塊晶片上,兩個相鄰的量子點也幾乎不可能是完全一樣的 [10]。

這種不可避免的「無序」(disorder)或「可變性」(variability)給大規模量子計算帶來了嚴峻的挑戰。如果每個量子位元的共振頻率都略有不同,那麼就無法使用一個統一的全局控制場(global control field)來同時操控它們,而必須為每一個量子位元單獨進行耗時的校準和調諧。對於一個百萬級量子位元的處理器來說,這種逐一校準的複雜度將是天文數字,使得系統的啟動和運行變得不切實際。

應對這一挑戰,研究界正從兩個方向同時推進,這也體現了量子計算從純物理研究向系統工程的轉變:

- 提升製造工藝的精度 (Manufacturing Process Control): 這是最根本的解決方案。其目標是利用最先進的半導體製造技術,從源頭上減少元件的物理差異。這正是英特爾等公司強調其300mm晶圓廠和極紫外光(EUV)微影技術等先進工藝的原因 [57, 58]。透過工業級的過程控制,可以最大限度地提高量子點陣列的幾何均勻性,從而降低其電學特性的離散度,提高良率(yield)[12, 35]。

- 發展自動化校準技術 (Automated Calibration): 這是務實的補充方案。它承認一定程度的非均勻性是不可避免的,並致力於開發能夠快速、自動地處理這種非均勻性的智能軟體。近年來,基於機器學習(Machine Learning)的自動調諧協議取得了顯著成功 [43, 44]。這些演算法可以自主地探索複雜的多維閘極電壓空間,在幾分鐘內自動完成一個量子點的形成和表徵,而這個過程如果由人工完成可能需要數小時甚至數天 [43]。將這種自動化技術擴展到大型陣列,有望實現對整個量子處理器的「一鍵式」校準。

未來,可擴展的量子計算機的實現,將依賴於這兩種方法的緊密結合:由先進製造提供盡可能均勻的硬體基礎,再由智能軟體來高效地管理和補償剩餘的非均勻性。這條硬體製造與智能控制軟體協同演進的道路,是克服均勻性挑戰、通往百萬量子位元時代的關鍵。

第六章:全球產業與研究態勢

半導體自旋量子位元領域的快速發展,得益於全球範圍內商業公司、學術機構和國家級研究計畫的共同推動。本章將梳理這一領域的主要參與者,比較不同技術路線的戰略定位,並分析台灣在其中的角色與佈局。

6.1 主要商業參與者

與超導和離子阱量子位元領域由IBM、Google、IonQ等巨頭引領的格局相似,半導體自旋量子位元領域也已湧現出幾個關鍵的商業參與者,它們正將學術研究成果轉化為工程化、可擴展的產品。

- 英特爾 (Intel): 作為全球半導體行業的領導者,英特爾的量子計算戰略明確地建立在其無與倫比的製造能力之上 [59, 60]。英特爾的核心賭注是,只有利用最先進的工業級CMOS製造技術(如300mm晶圓和EUV微影),才能解決量子計算最終面臨的規模化和均勻性挑戰 [12, 57]。公司已經開發出多代矽自旋量子位元研究晶片,如12量子位元的「Tunnel Falls」,並積極與學術界合作(如馬里蘭大學的LQC),旨在透過提供標準化的高品質晶片來推動整個生態系統的發展,從而加速研究進程並培養下一代量子工程師 [57, 58]。

- Diraq: 這家位於澳洲雪梨的新創公司,是從全球最頂尖的矽量子計算研究中心之一——新南威爾斯大學(UNSW)分拆而來,由該領域的先驅Andrew Dzurak教授領導 [61]。Diraq的競爭優勢在於其長達二十年的研究積累和一系列關於CMOS量子點技術的核心專利 [61, 62]。他們的技術路線強調利用標準CMOS工藝實現與控制電路的緊密集成,目標是最終在單一晶片上實現數百萬乃至數十億個量子位元 [61]。Diraq採取了開放合作的生態系統戰略,與比利時的頂尖半導體研究機構imec合作進行晶片製造,與Emergence Quantum合作開發Cryo-CMOS技術,並與NVIDIA合作利用AI和GPU加速量子系統的校準和控制,展示了其整合全球頂尖資源的決心 [34, 44, 56]。

- Quantum Motion: 這是一家總部位於英國的知名新創公司,其創始團隊同樣來自牛津大學和倫敦大學學院的頂尖學術實驗室。Quantum Motion的願景是開發一種「基於無處不在的矽技術的可擴展量子位元陣列」[63]。他們的核心理念與英特爾和Diraq一致,即量子計算的最終勝利將取決於可擴展性,而矽是實現這一目標的最佳平台。他們強調,如果不採用像矽這樣可大規模集成的技術,未來的量子計算機可能會是「體育場大小」而非「郵票大小」。Quantum Motion已與世界領先的晶圓代工廠GlobalFoundries建立合作關係,共同開發與標準矽工藝兼容的量子計算架構 [63]。

除了這些專注於自旋量子位元的公司外,一些科技巨頭如Google、IBM和Microsoft雖然其主要的硬體路線是超導或拓撲量子位元,但它們在量子演算法、控制軟體和糾錯碼方面的研究對整個量子計算領域都具有深遠影響,其開發的控制系統和軟體框架也可能被應用於自旋量子位元平台 [59, 64, 65]。

表2:半導體自旋量子位元領域主要公司概覽

| 公司 |

主要技術路線 |

關鍵成就 / 晶片 |

戰略定位與主要合作夥伴 |

| 英特爾 (Intel) |

Si-MOS, 電子自旋量子位元 |

Tunnel Falls (12-qubit), 300mm晶圓製造 |

利用頂尖半導體製造能力;透過研究合作夥伴關係(如LQC)推動生態系統 |

| Diraq |

Si-MOS, 電子自旋量子位元 |

>1K高溫操作, Cryo-CMOS集成 |

基於CMOS原生設計實現大規模擴展;擁有核心IP組合;合作夥伴: imec, Emergence Quantum, NVIDIA |

| Quantum Motion |

矽基量子位元 |

可擴展陣列架構 |

強調與普遍存在的矽技術的兼容性;合作夥伴: GlobalFoundries |

此表清晰地勾勒出主要參與者的競爭態勢。儘管它們都選擇了矽這條賽道,但其公開的戰略重點和合作模式略有不同。英特爾強調其內部的、垂直整合的製造實力;Diraq則突出其基礎IP和一個廣泛的、合作驅動的生態系統模式;Quantum Motion則聚焦於向外界傳達其技術與標準矽工藝兼容的核心訊息。這有助於理解各方為解決可擴展性問題所採取的不同策略。

6.2 全球重點研究機構與國家級計畫

在商業公司將技術推向市場的同時,全球的頂尖學術機構和國家級研究計畫仍在持續不斷地貢獻著基礎科學的突破和前沿技術的探索,它們是整個領域創新的源頭。

- 全球研究中心: 在學術界,有幾個研究中心長期以來引領著半導體自旋量子位元的發展。日本的理化學研究所(RIKEN),在Seigo Tarucha教授的領導下,是該領域的開創者之一,在量子位元的高保真度操控、讀取以及與超導諧振腔的耦合方面做出了大量奠基性工作 [29]。瑞士的國家能力研究中心SPIN(NCCR SPIN)是一個由政府資助的大型跨機構合作項目,匯集了巴塞爾大學、蘇黎世聯邦理工學院等頂尖機構的研究力量,專注於矽和鍺自旋量子位元的物理、材料和可擴展性研究,特別是在電洞自旋量子位元方面處於世界領先地位 [66]。此外,澳洲的新南威爾斯大學(UNSW)、荷蘭的QuTech(由台夫特理工大學和TNO聯合創立)、法國的CEA-Leti等,也都是該領域公認的世界級研究重鎮。

- 台灣的國家級佈局: 台灣作為全球半導體產業的領導者,自然不會在下一代計算技術的競賽中缺席。台灣政府已經啟動了國家級的「埃世代半導體計畫」,其中一個重要的分項計畫就是「矽基量子計算次系統開發」[54]。該計畫旨在利用台灣在半導體研發、設計和製造方面的既有優勢,整合產學研力量,開發台灣自己的量子計算機。計畫設定了明確的目標:在2025年實現一個2量子位元的運算系統,單量子位元保真度達到80%,並在2030年時追趕上歐美領先群體 [54]。這個計畫的關鍵組成部分包括開發量子位元晶片本身,以及至關重要的低溫CMOS(Cryo-CMOS)控制/讀取電路次系統 [54, 55]。這項國家級的戰略投入,不僅旨在為台灣在後摩爾定律時代保持半導體產業的領先地位尋找新的增長點,也為國內的學術機構如陽明交通大學、台灣大學和研究機構如台灣半導體研究中心(TSRI)提供了重要的研究平台和方向 [55, 67, 68]。

6.3 橫向比較:與超導及離子阱量子位元的優劣勢分析

要全面評估半導體自旋量子位元的地位,必須將其與另外兩個領先的量子計算平台——超導量子位元和離子阱量子位元——進行橫向比較。這三者各有千秋,目前尚無任何一個平台在所有關鍵指標上都佔據絕對優勢。

- 超導量子位元 (代表: Google, IBM, Rigetti):

- 優勢: 核心優勢在於極快的閘極操作速度(通常在幾十奈秒量級),這使得它們能夠在相干時間內執行更多的操作。技術相對成熟,目前在量子位元數量上處於領先地位,已有超過千位元的處理器問世 [13, 64, 69, 70]。

- 劣勢: 量子位元的物理尺寸較大(約毫米級),限制了單晶片的集成密度。相干時間相對較短(通常在幾百微秒量級)。需要極低的運行溫度(低於20毫開爾文),對製冷設備的要求極高。量子位元之間的連接性通常是固定的,僅限於最近鄰,這給複雜演算法的編譯帶來了挑戰 [10, 71, 72]。

- 離子阱量子位元 (代表: IonQ, Quantinuum):

- 優勢: 核心優勢在於卓越的量子位元質量。作為天然的原子,所有量子位元都是完美的全同粒子。它們被懸浮在超高真空中,與環境極度隔離,因此擁有極長的相干時間(可達秒級甚至分鐘級)和極高的操作保真度。在單個離子阱內,可以實現全對全的連接性,這對許多量子演算法非常有利 [10, 11, 69]。

- 劣勢: 主要瓶頸是極慢的閘極操作速度(通常在微秒到毫秒量級),比超導量子位元慢約1000倍。這限制了在相干時間內能夠完成的計算深度。此外,系統的可擴展性面臨巨大挑戰,在單個阱中囚禁和精確控制大量離子變得非常困難,而將多個阱連接起來的技術也極其複雜 [10, 11, 72]。

- 半導體自旋量子位元 (代表: Intel, Diraq):

- 優勢: 核心優勢在於極小的物理尺寸(約百奈米級)和基於CMOS工藝的巨大可擴展性潛力。在同位素純化矽中可以實現非常長的相干時間。其運行溫度(約100mK至1K)相比超導量子位元的要求略為寬鬆,有利於控制電路的集成 [6, 10]。

- 劣勢: 歷史上,其操作保真度(特別是雙量子位元閘)一直落後於前兩者,儘管近年來已追趕上來。元件的均勻性是一個巨大的工程挑戰。連接性受限於最近鄰,需要依賴穿梭等先進技術來實現遠距離交互 [10]。

表3:主要量子位元平台的關鍵指標比較

| 指標 |

半導體自旋量子位元 |

超導量子位元 |

離子阱量子位元 |

| 物理尺寸 |

奈米 (nm) |

毫米 (mm) |

原子 |

| 擴展路徑 |

CMOS製造 |

晶片間互聯 |

網絡化離子阱 / 穿梭 |

| 閘極速度 (2Q) |

快 (10s-100s ns) |

非常快 (約10s ns) |

慢 (µs-ms) |

| 相干時間 (T₂) |

非常長 (在矽中) |

短-中 (約100s µs) |

極長 (秒級以上) |

| 保真度 (2Q) |

>99% (持續提升) |

>99% |

>99% |

| 連接性 |

局部 (穿梭實現遠程) |

固定、局部 |

全對全 (在阱內) |

| 運行溫度 |

~100mK - 1K |

<20 mK |

室溫 (真空室) |

這張比較表揭示了一場多維度的技術競賽,不存在絕對的贏家。超導量子位元是「速度之王」,離子阱是「品質之王」,而半導體自旋量子位元則是潛在的「規模之王」。這場競賽的最終勝者,將是那個能夠最好地彌補自身短板,同時將核心優勢發揮到極致的平台。對於半導體自旋量子位元而言,其前進的道路非常清晰:在保持並發揮其無與倫比的可擴展性優勢的同時,繼續提升操作保真度和連接性,以期在綜合性能上達到或超越其競爭對手。

第七章:結論與未來展望

經過二十多年的深入研究與快速發展,半導體自旋量子位元已經從一個新穎的物理概念,成長為構建大規模量子計算機的最有力競爭者之一。它與現代半導體工業的深度融合,為其描繪了一條通往百萬量子位元處理器的、看似最為現實的技術藍圖。然而,在這條道路上,依然存在著若干核心挑戰需要克服。本章將總結這些挑戰,展望近期的發展趨勢,並對該技術在量子計算領域的最終潛力做出評估。

7.1 當前核心挑戰總結

儘管在單個或少量量子位元的性能上取得了巨大成功,但要將半導體自旋量子位元擴展到能夠解決實際問題的規模,仍需應對三大系統級的挑戰:

- 規模化下的質量與均勻性 (Quality and Uniformity at Scale): 這是最核心的挑戰。如何在工業化量產的過程中,保證數百萬個奈米級量子點的電學特性高度一致,並維持高良率,是一個巨大的製造科學難題 [6, 10]。目前,即使是最好的製造工藝也無法避免元件間的微小差異,這導致了對複雜、耗時的單獨校準的需求。未來的突破將依賴於更先進的製造過程控制與基於人工智能的快速自動化校準技術的結合 [43, 44]。

- 連接性與控制 (Connectivity and Control): 在一個密集的二維量子位元陣列中,如何有效地在任意兩個量子位元之間建立連接,並精確地對它們進行定址和操控,是另一個關鍵瓶頸。雖然量子位元穿梭技術為解決連接性問題提供了可行的方案,但實現高保真度、低串擾的長距離穿梭仍需進一步優化 [41, 47]。與此同時,解決控制線路「扇出問題」的低溫CMOS(Cryo-CMOS)集成技術,雖然方向明確,但在超低功耗、低雜訊電路的設計與製造上仍有大量工程工作需要完成 [52, 53]。

- 量子糾錯的系統集成 (System Integration for Quantum Error Correction): 實現容錯量子計算的最終目標,不僅僅是將高質量的元件簡單地組合在一起。它要求將高保真度的初始化、單/雙量子位元閘、以及快速讀取等所有環節,無縫集成到一個能夠執行量子糾錯碼(如表面碼)的完整系統中 [46, 73]。這需要極快的測量和古典計算反饋迴路,以便在量子態退相干之前檢測並糾正錯誤。將所有這些高性能組件在一個大型系統中協同工作,並達到糾錯所需的整體性能標準,是物理、工程和計算機科學交叉領域的終極挑戰 [50]。

7.2 近期發展趨勢:從量子模擬到容錯計算

面對上述挑戰,該領域的發展正呈現出從基礎元件性能演示,向更複雜的系統級功能驗證的清晰趨勢。

在近期(1-3年內),一個重要的發展方向是利用中等規模(數十個量子位元)的自旋量子位元處理器作為量子模擬器 [10]。這些處理器雖然還不足以執行像Shor演算法這樣的大規模演算法,但它們已經足夠強大,可以用來模擬一些傳統計算機難以處理的、特定量子系統的行為,例如材料科學中的磁性模型或量子化學中的分子動力學。最近,研究人員已經成功地在一個6量子位元的矽自旋處理器上,運行了用於研究多體物理中「動力學量子相變」的量子線路,這標誌著該平台在量子模擬應用上的初步成功 [45, 74]。

在中期(3-5年內),研究的焦點將轉向在二維陣列(如2xN結構)上演示量子糾錯的基本構建模塊 [10, 46]。這包括重複地執行表面碼的穩定器測量循環,以展示系統能夠檢測錯誤並延長一個邏輯量子位元的壽命。這類實驗將是對系統集成度、控制精度和反饋速度的終極考驗,也是通往容錯計算的關鍵里程碑 [18, 75]。

7.3 半導體自旋量子位元在量子計算領域的最終潛力

半導體自旋量子位元的最終潛力,根植於其與人類歷史上最成功的製造技術——半導體CMOS技術——的共生關係 [1, 13]。這條技術路徑的終極願景,不僅僅是建造一台量子計算機,而是建造一台在形態和製造方式上都極其類似於現代微處理器的量子計算機:一個在單一矽晶片上高密度集成了數百萬甚至數十億個量子位元的、可大規模生產的集成電路 [12, 61, 63]。

這個願景賦予了半導體自旋量子位元一條獨特的、其他平台難以複製的發展路徑。它的成功,可能最終將不那麼依賴於基礎物理學的顛覆性突破,而更多地取決於在製造科學、材料工程、控制軟體和系統架構等領域的持續、漸進式的工程創新。這是一場將半導體工業在過去半個世紀裡積累的、用於駕馭數十億電晶體的龐大知識體系和精密工具,應用於駕馭數十億量子位元的宏偉工程。

儘管前方的工程障礙依然巨大,但這條道路是清晰的。從實驗室中的單個「英雄」量子位元,到工業晶圓廠中均勻、高良率的量子位元陣列;從笨拙的手動調諧,到由人工智能驅動的「一鍵式」全自動校準;從雜亂的低溫接線,到與量子晶片緊密集成的低溫CMOS控制系統。每一步進展,都在將量子計算從一個遙遠的科學夢想,變為一個觸手可及的工程現實。在通往通用容錯量子計算的漫長征途中,半導體自旋量子位元憑藉其與矽的強大聯盟,無疑是最有希望率先衝過終點線的選手之一。

▲

王培儒

王培儒