整體系統集成、挑戰與未來展望

Ref: Delft circuit

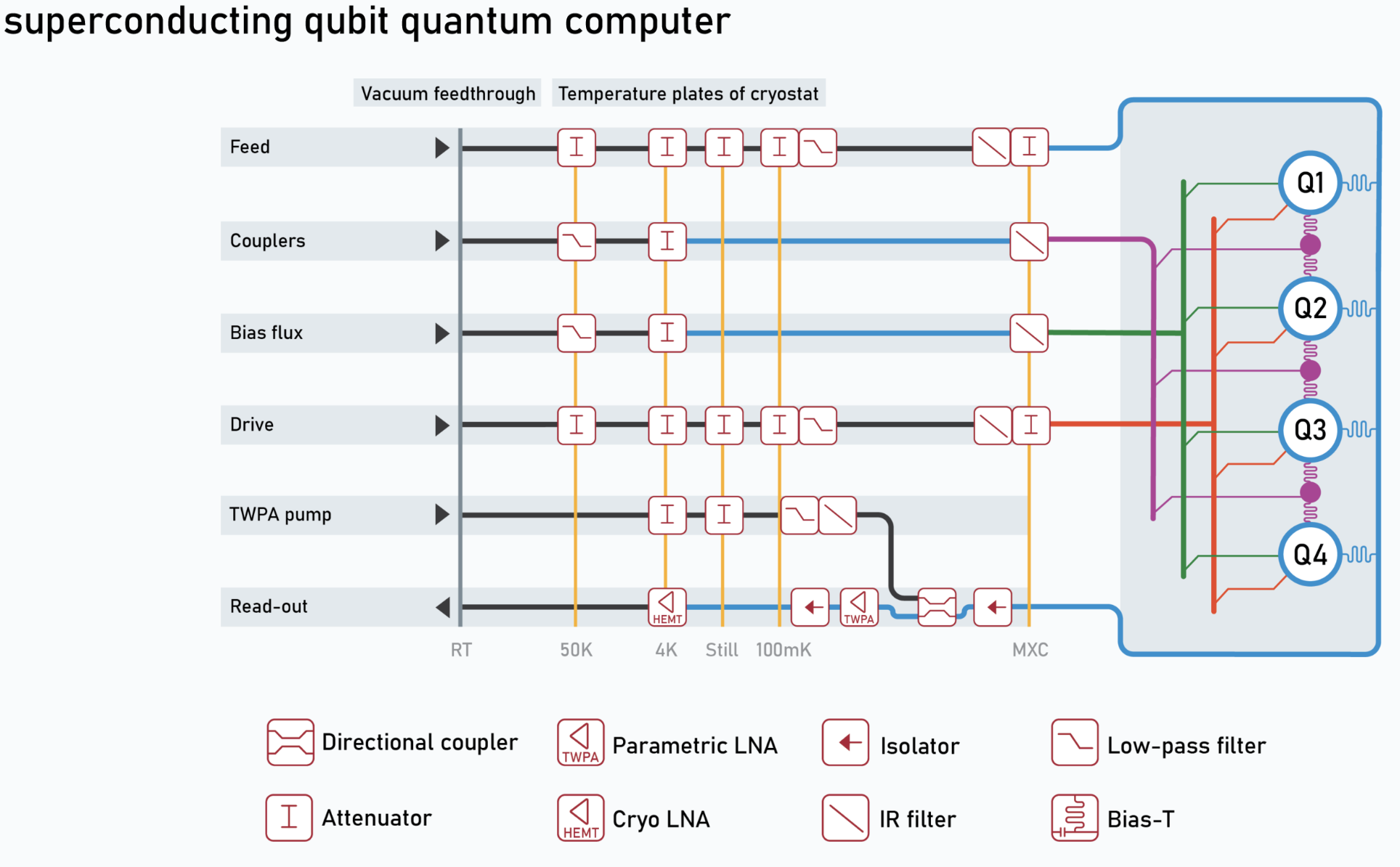

完整的超導量子電腦至少需包含:氦3極低溫真空環境、冷卻系統、大量的射頻訊號控制與讀取儀器等,故當前的超導量子電腦非常的巨大。此外,一個量子位元至少需要四條線路:

- 控制頻率*1:挑控磁通量的Fluxline。

- 控制狀態*1:Driveline。

- 讀取狀態*2:讀出 line一進一出。

https://arxiv.org/pdf/1612.08208

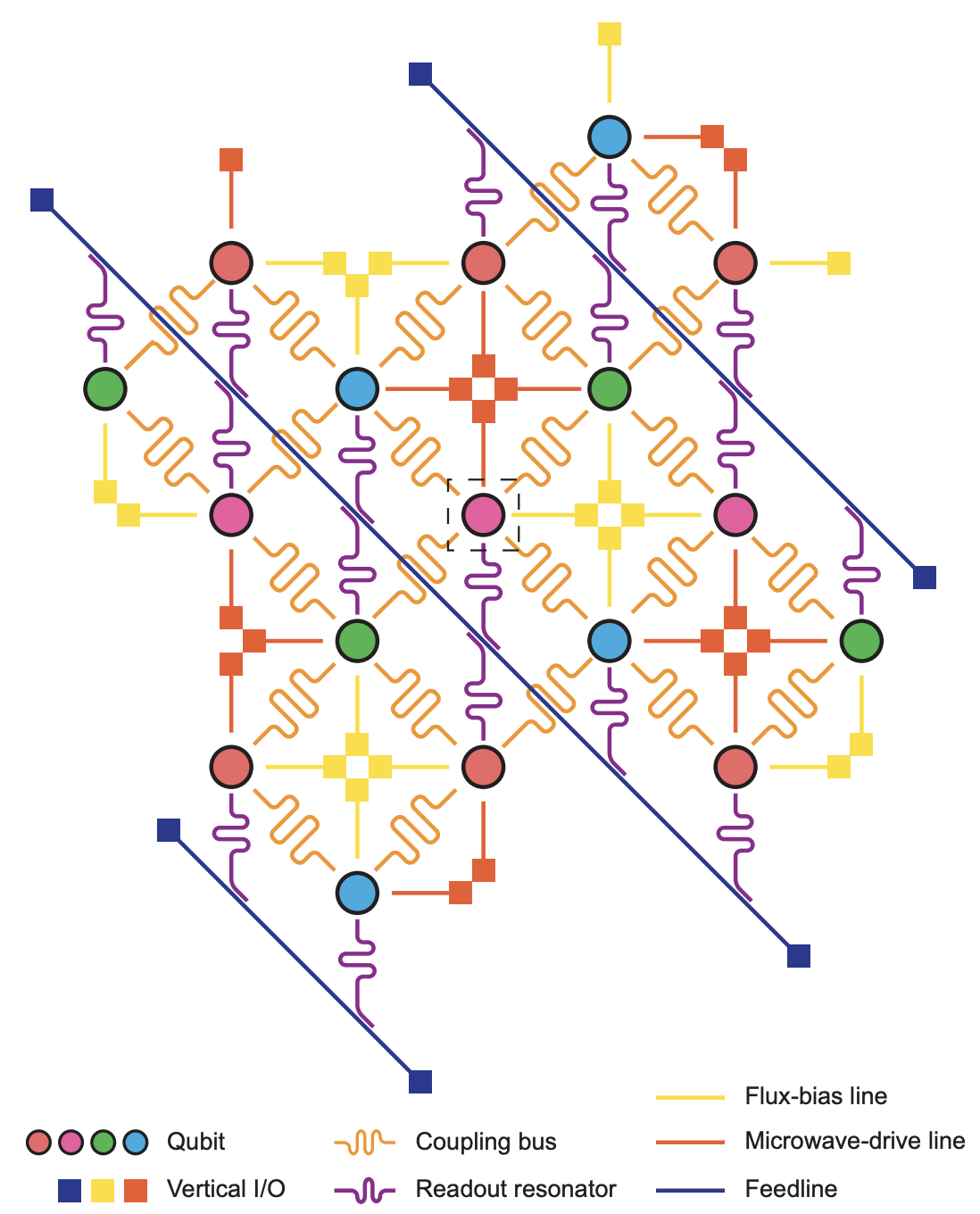

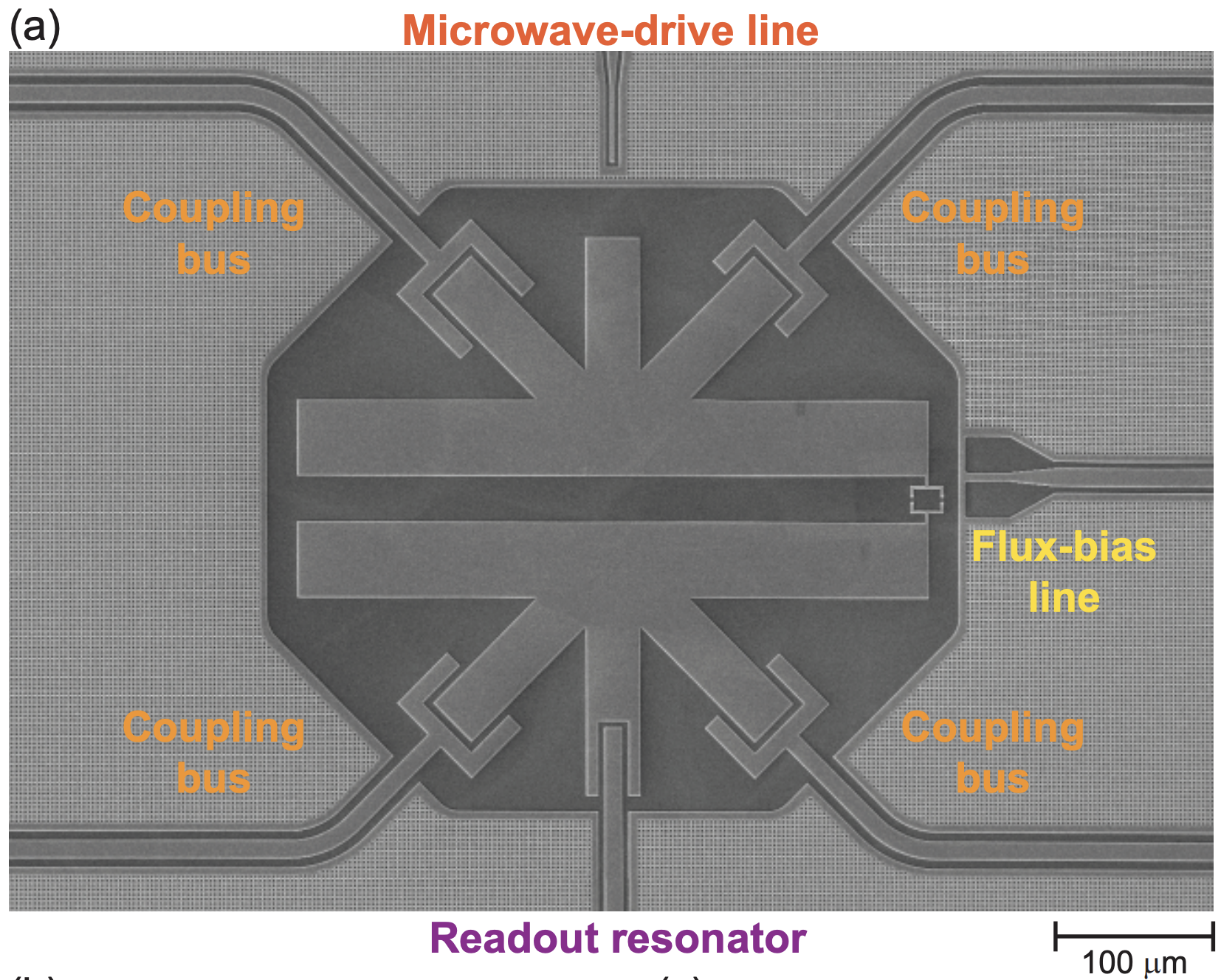

▲要達到量子計算,需要同時操作許多 Qubit,同時因為糾錯的關係,也需要額外的 Qubit 來進行糾錯。上圖是一個 17 位元的實驗性量子晶片,排列方式是一種稱為 surface code(表面碼)的量子糾錯型態,原形為 Qubit,粉色及紅色是 Data Qubit,天藍色及綠色是 Check Qubit。每個 Qubit 都連接 7 條線(暱稱為 Starmon),其中 4 條為 Qubit 間耦合、1 條 Flux line、1 條 Drive line、1 條 讀出 諧振器。讀出讀出 諧振器 分別併入到三條 feedline。雖然當前的技術可以將多個Qubit的讀出 line整合在一起,透過頻率隔離的技術共用同一條讀出 line(所謂Feedline),但我們還需要考慮控制量子位元間交互作用的Resonator,一個100位元的量子電腦原型就需要400條線路從外部送入,故目前常見的超導量子電腦可以看見大量的線路。

arxiv: 2408.12433

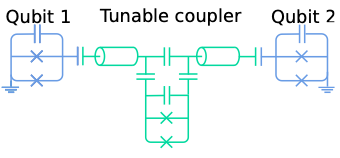

量子位元間交互作用的Resonator/Coupler可以是可調控的,可進一步調控不同Qubit之間的耦合強度,但亦會增加控制電路的複雜度。

IV. 整體系統集成、挑戰與未來展望

構建一台功能強大的超導量子電腦,不僅僅是將各個高性能組件簡單堆砌,更是一個涉及深度系統集成的複雜工程。硬體與軟體之間、各個子系統之間都存在著緊密的相互依賴關係。

A. 硬體與軟體組件間的相互依賴性

量子電腦是一個高度耦合的系統,其任何一部分的特性都會深遠影響其他部分。QPU的特性,如量子位元類型、數量、保真度、連接性以及雜訊水平,直接決定了控制脈衝的設計複雜度、量子糾錯碼的選擇與效率、編譯器優化的策略,乃至於哪些類型的量子演算法在該平台上是可行的 [46, 67, 68, 70]。例如,一個具有特定二維佈局和鄰近連接的QPU可能更適合運行表面碼進行糾錯。

反過來,低溫系統的能力,如總冷卻功率、可用空間和佈線容量,也直接限制了QPU的潛在規模以及控制和讀出電子設備的集成方式 [11, 35]。如果低溫系統無法支持更多量子位元產生的熱量或容納相應的控制線路,那麼即使QPU製造技術有所突破,系統的整體性能也無法提升。

這種相互依賴性意味著量子電腦的發展不能僅僅依靠單個組件的孤立改進,而必須進行整個技術堆疊的協同優化。一個領域的進步(例如,量子位元相干時間的顯著提高)可能會對其他領域提出新的需求或暴露出新的瓶頸(例如,需要更快、更精確的控制和讀出系統,或更複雜的量子糾錯解碼器)。「全棧」(full-stack) 的概念 [68, 70] 本身就強調了這些組件間的緊密聯繫。例如,「物理感知全棧軟體」(Physics-Aware, Full-Stack Software) [70] 的理念,正是要讓軟體層面充分理解和利用底層物理硬體的特性。Cryo-CMOS技術的發展也是一個例證,它試圖將控制電子與低溫系統更緊密地集成起來,以解決佈線和延遲問題 [6, 11]。

B. 構建可擴展超導量子電腦的主要瓶頸

儘管超導量子計算在過去幾年中取得了顯著進展,但要實現大規模、可容錯的量子計算,仍面臨諸多嚴峻瓶頸:

- 量子位元的品質與可擴展性: 這是最核心的挑戰。實現大量具有高相干時間、高閘保真度和高讀出保真度的量子位元,並且能夠以一致的、可重複的方式進行製造,仍然極其困難 [1, 5, 6, 7]。

- 量子糾錯的巨大開銷: 實現一個容錯的邏輯量子位元需要數百甚至數千個物理量子位元,這種巨大的資源冗餘是目前實現容錯計算的最大障礙之一 [6, 63, 64]。

- 大規模佈線與互連的挑戰 (「佈線問題」): 如何將成千上萬條控制和讀出訊號線路從室溫引入到極低溫的稀釋製冷機內部,同時有效管理由此產生的熱負載、確保訊號完整性並避免串擾,是一個極其棘手的工程難題 [6, 33, 35]。

- 低溫系統的可擴展性: 現有的稀釋製冷機在為未來可能包含數百萬量子位元及其相關控制電子的系統提供足夠的冷卻功率方面面臨挑戰 [11]。

- 高昂的成本: 從QPU的研發和製造,到稀釋製冷機、精密控制與讀出電子設備、特殊低溫線纜的採購,再到整個系統的運行和維護,都耗資巨大,限制了技術的普及和發展速度 [3, 12, 13, 20, 39]。

雖然量子位元的數量經常成為衡量進展的頭條新聞 [2],但那些看似不那麼「光鮮」的方面,如低溫佈線的密度和熱管理、控制訊號的生成與傳輸質量,以及量子糾錯所需的巨大物理資源開銷,對於實現真正大規模、可容錯的量子計算而言,其瓶頸效應可能同等重要,甚至更為顯著。如果這些支持性組件的發展跟不上量子位元數量的增長,那麼僅僅增加量子位元數量並不能帶來實質性的計算能力提升。

C. 當前趨勢與未來預測

展望未來,超導量子計算領域呈現出以下幾個主要發展趨勢:

- 持續提升量子位元數量與質量: IBM、Google等領先者將繼續致力於開發具有更多量子位元和更高性能(如更長相干時間、更高保真度)的QPU [1, 2, 6]。

- 聚焦錯誤緩解與早期量子糾錯實現: 在NISQ時代,重點是通過先進的錯誤緩解技術使現有嘈雜設備更加實用,同時積極探索和實現初步的量子糾錯方案,為最終實現容錯計算鋪平道路。Google的Willow晶片集成表面碼糾錯 [1] 和SurgeonQ等合作項目 [45] 正是這一趨勢的體現。

- Cryo-CMOS技術的發展: 將部分控制電子集成到低溫環境中,更靠近量子位元,以減少佈線複雜性、降低延遲和熱負載,是提升系統性能和可擴展性的重要方向 。

- 模組化量子架構探索: 為了克服單個晶片在尺寸和複雜性上的限制,研究人員正在探索通過高速互連技術將多個QPU晶片或模組連接起來,構建更大規模的量子計算系統 。

- 混合量子-經典架構的持續主導: 在可預見的未來,特別是在NISQ設備上解決實際問題時,量子計算機將作為協處理器與經典高性能計算機協同工作。因此,針對這種混合架構的硬體和軟體協同設計仍將是關鍵 。

- 量子雲平台的增長: 越來越多的量子硬體資源將通過雲平台提供給用戶,降低了用戶接觸和使用量子計算的門檻,促進了應用探索和生態系統的發展 。

- 國家級戰略投入的持續加強: 美國、中國、歐盟等主要國家和地區將繼續加大對量子計算領域的戰略性投入,支持基礎研究、技術開發和人才培養 。

短期內,量子計算的發展可能會主要集中在通過改進錯誤緩解技術和混合演算法來提升NISQ系統的實用性。而長遠目標則始終是通過穩健的量子糾錯實現大規模的容錯量子計算。架構趨勢方面,一方面是向著更高程度的集成化發展(如Cryo-CMOS),另一方面也可能通過模組化來突破單晶片擴展的物理極限。這些都是在應對當前局限性的同時,為實現量子計算的最終潛力所採取的務實步驟。

V. 結論與主要觀點

構建一台實用的、可擴展的超導量子電腦是一項極其複雜的跨學科系統工程,它融合了量子物理、材料科學、微波工程、低溫工程、軟體工程等多個領域的尖端知識,並且需要巨大的資金投入。從核心的量子處理器 (QPU) 到極端的低溫環境,再到精密的控制與讀出系統、特製的低溫佈線,以及複雜的軟體堆疊,每一個環節都至關重要,且面臨著獨特的技術挑戰。

儘管過去幾年取得了令人鼓舞的進展,例如量子位元數量的增加和相干時間的提升,但通往實用化超導量子計算的道路依然漫長。在硬體層面,量子位元的質量和一致性、大規模佈線的散熱與訊號完整性、以及低溫系統的冷卻能力擴展等問題仍是主要的瓶頸。在軟體層面,開發高效的雜訊感知演算法、構建穩健的量子中間表示和編譯器、以及實現資源開銷可控且能實時運行的量子糾錯協議,都是亟待突破的難關。

這項事業的成功,並非單個組件的突破所能保證,而是依賴於整個複雜系統中所有組成部分的協同進步和整體優化。當前全球範圍內的研發格局,既體現了主要科技強國和領先企業之間的激烈競爭,也反映出在應對這些巨大挑戰時,學術界、產業界和政府之間開展合作的必要性。

最終,能否開發出穩健的量子糾錯方案並成功擴展高質量的量子位元系統,將是決定超導量子計算能否實現其革命性潛力的關鍵所在。這是一場需要持續創新、耐心投入和全球協作的「馬拉松」。

超導電腦部件及其主要廠商(再次更新版)

| 部件類別 | 具體部件/服務 | 主要廠商/機構 (根據提供的HTML內容) |

|---|---|---|

| 量子處理器 (QPU) / 量子晶片 | QPU 標準產品及代工服務 |

|

| QPU 內部開發/研究 (大型集成商/研究機構) |

|

|

| 低溫系統 | 稀釋製冷機 / 低溫製冷系統 |

|

| 控制與讀取電子設備 | 控制電子系統 (專用平台/模塊化系統/脈衝產生器) |

|

| 讀出與測量系統組件 |

|

|

| 特殊導線與接頭 | 低溫導線 (同軸電纜, 柔性線纜, 雙絞線, 光纖硬體/選項) |

|

| 低溫連接器/接頭 (RF接頭, 高密度接頭, 氣密接頭/饋通) |

|

|

| 輔助系統部件 | 真空系統部件 (真空幫浦, 真空計, 閥門等) |

|

| 磁屏蔽與輻射屏蔽 / 低溫探針台 |

|

|

| 完整系統提供商 | 提供完整超導量子計算系統或解決方案 |

|

王培儒

王培儒